- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄373771 > Z8S180 (ZiLOG, Inc.) CAP 0.1UF 100V +80-20% Z5U AXIAL TR-14 PDF資料下載

參數(shù)資料

| 型號(hào): | Z8S180 |

| 廠商: | ZiLOG, Inc. |

| 英文描述: | CAP 0.1UF 100V +80-20% Z5U AXIAL TR-14 |

| 中文描述: | 強(qiáng)化Z180微處理器 |

| 文件頁(yè)數(shù): | 60/70頁(yè) |

| 文件大?。?/td> | 387K |

| 代理商: | Z8S180 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)當(dāng)前第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)

Z80180/Z8S180/Z8L180

Enhanced Z180 Microprocessor

Zilog

1-60

P R E L I M I N A R Y

DS971800401

Opcode is fetched during the interrupt acknowledge cycle

for INT

0

when Mode 0 is used.

When

Z80180/Z8S180/Z8L180 operates as follows:

a

TRAP

interrupt

occurs,

the

1.

The TRAP bit in the Interrupt TRAP/Control (ITC)

register is set to 1.

2.

The current PC (Program Counter) value, reflecting

the location of the undefined Opcode, is saved on the

stack.

3.

The Z80180/Z8S180/Z8L180 vectors to logical

address 0. Note that if logical address 0000H is

mapped to physical address 00000H, the vector is the

same as for RESET. In this case, testing the TRAP bit

in ITC will reveal whether the restart at physical

address 00000H was caused by RESET or TRAP.

All TRAP interrupts occur after fetching an undefined sec-

ond Opcode byte following one of the “prefix” Opcodes

CBH, DDH, EDH, or FDH, or after fetching an undefined

third Opcode byte following one of the “double prefix” Op-

codes DDCBH or FDCBH.

The state of the Undefined Fetch Object (UFO) bit in ITC

allows TRAP software to correctly “adjust” the stacked PC,

depending on whether the second or third byte of the Op-

code generated the TRAP. If UFO=0, the starting address

of the invalid instruction is equal to the stacked PC-1. If

UFO=1, the starting address of the invalid instruction is

equal to the stacked PC-2.

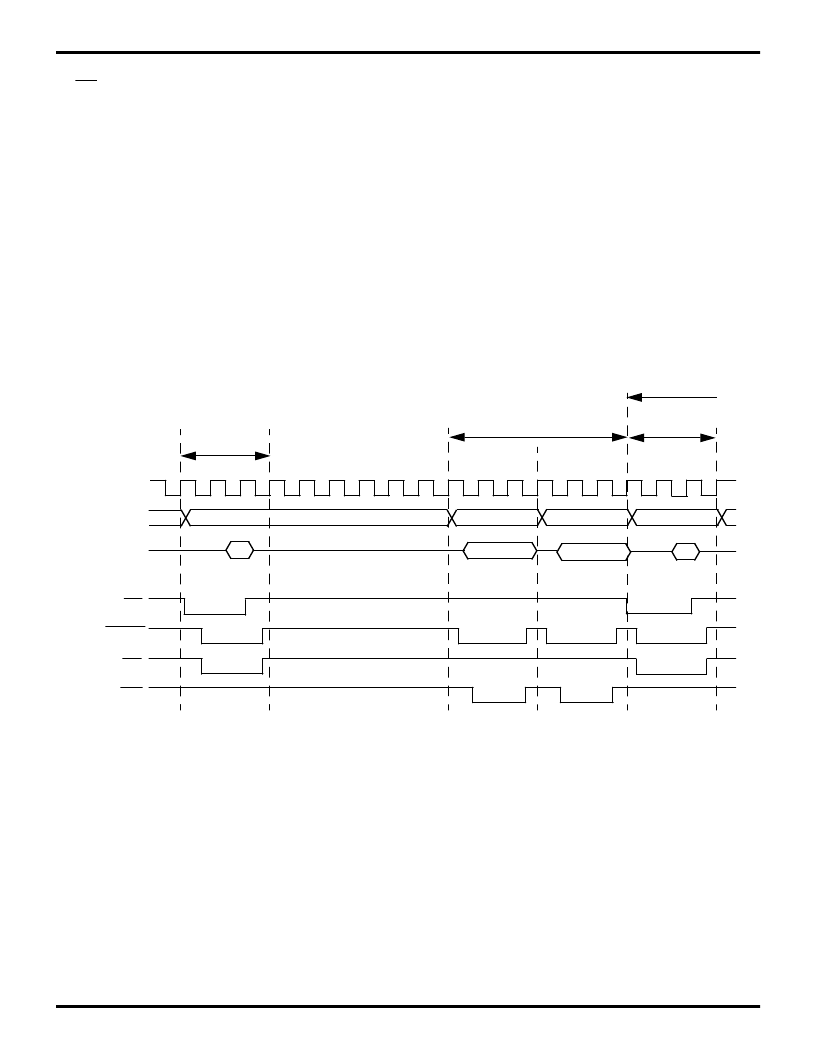

Figure 76. TRAP Timing-2

nd

Opcode Undefined

T

1

T

2

T

3

T

TP

T

i

T

i

T

i

T

i

T

i

T

1

T

2

T

3

T

2

T

3

T

1

T

1

T

2

A

0

-A

18

(A

19

)

φ

D

0

-D

7

PC

0000H

SP-1

Undefined

Opcode

MREQ

M1

RD

WR

T

3

SP-2

PC

H

PC

L

2nd Opcode

Fetch Cycle

PC Stacking

Opcode

Fetch Cycle

Restart

from 0000H

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| Z8S18006FEC | CAP 1UF 50V 10% X7R AXIAL TR-14 |

| Z8S18006FSC | CAP 0.47UF 50V 10% X7R AXIAL TR-14 |

| Z8S18006PEC | CAP 0.1UF 50V 2% NP0(C0G) AXIAL TR-14 |

| Z8S18006PSC | CAP 1000PF 100V 5% NP0(C0G) DIP-2 TUBE |

| Z90102 | CAP 560PF 100V 10% X7R AXIAL BULK R-MIL-PRF-39014 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| Z8S18000ZCO | 功能描述:開(kāi)發(fā)板和工具包 - 其他處理器 Z8S180 App Board RoHS:否 制造商:Freescale Semiconductor 產(chǎn)品:Development Systems 工具用于評(píng)估:P3041 核心:e500mc 接口類(lèi)型:I2C, SPI, USB 工作電源電壓: |

| Z8S18000ZEM | 功能描述:仿真器/模擬器 Z8S180 Emulator Kit RoHS:否 制造商:Blackhawk 產(chǎn)品:System Trace Emulators 工具用于評(píng)估:C6000, C5000, C2000, OMAP, DAVINCI, SITARA, TMS470, TMS570, ARM 7/9, ARM Cortex A8/R4/M3 用于:XDS560v2 |

| Z8S18006FEC | 制造商:ZILOG 制造商全稱(chēng):ZILOG 功能描述:ENHANCED Z180 MICROPROCESSOR |

| Z8S18006FSC | 制造商:ZILOG 制造商全稱(chēng):ZILOG 功能描述:ENHANCED Z180 MICROPROCESSOR |

| Z8S18006PEC | 制造商:ZILOG 制造商全稱(chēng):ZILOG 功能描述:ENHANCED Z180 MICROPROCESSOR |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。