- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373785 > ZL50012 (Zarlink Semiconductor Inc.) Flexible 512-ch Digital Switch PDF資料下載

參數(shù)資料

| 型號: | ZL50012 |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | Flexible 512-ch Digital Switch |

| 中文描述: | 靈活的512通道數(shù)字開關(guān) |

| 文件頁數(shù): | 20/65頁 |

| 文件大小: | 1145K |

| 代理商: | ZL50012 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁

ZL50012

Data Sheet

23

Zarlink Semiconductor Inc.

2.3.3 Fractional Input Bit Delay Programming

In addition to the input bit delay feature, the device allows users to change the sampling point of the input bit. By

default, the sampling point is at 3/4 bit. Users can change the sampling point to 1/4, 1/2, 3/4 or 4/4 bit position by

programming Bit 3 and 4 of the Stream Input Control Registers (SICR).

Figure 16 - Input Bit Delay Timing Diagram

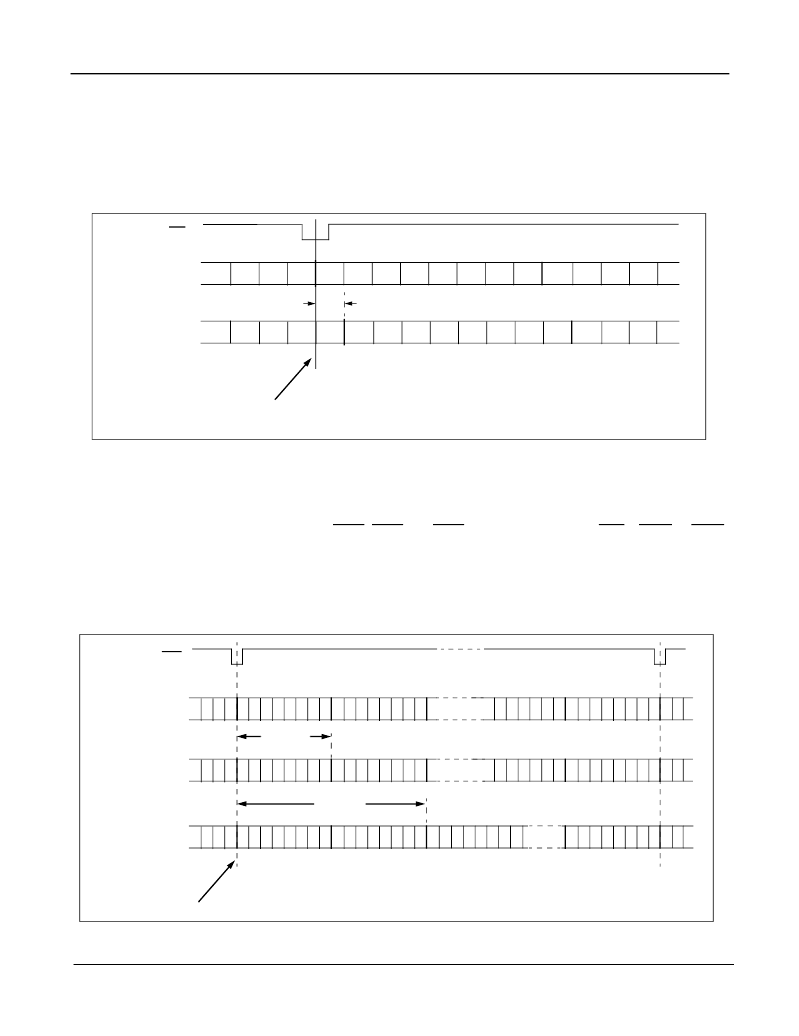

2.3.4 Output Channel Delay Programming

This feature allows each output stream to have a different output frame boundary with respect to the output frame

boundary defined by the output frame pulse (FPo0, FPo1 and FPo2) and the output clock (CKo0, CKo1 or CKo2).

By default, all output streams have zero channel delay such that Ch 0 is the first channel that appears after the

output frame boundary as shown in Figure 17. Different output channel delay can be set by programming Bit 5 to 11

in the Stream Output Offset Registers (SOOR). The output channel delay can vary from 0 to 31, 0 to 63 and 0 to

127 for the 2.048 Mb/s, 4.096 Mb/s and 8.192 Mb/s modes respectively.

Figure 17 - Output Channel Delay Timing Diagram

FPi

7

2

3

4

5

6

1

0

STi

X

Bit Delay = 0

(Default)

Ch0

7

4

5

6

Ch1

2

3

1

0

7

2

3

4

5

6

1

0

STi

X

Bit Delay = 1

Ch0

7

5

6

Ch1

2

3

1

0

Last Channel

Last Channel

Bit Delay = 1

Note: Last Channel = 31, 63, 127 for 2.048 Mb/s, 4.096 Mb/s and 8.192 Mb/s mode respectively

Input Frame Boundary

Note:

X

= 0 to 15

4

FPo

7

2

3

4

5

6

1 0

Channel Delay = 0

Ch 0

7

2

3

4

5

6

1 0

Ch 1

2

3

1 0

7

2

3

4

5

6

1 0

Last Channel

2

3

4

5

6

1 0

Last Channel -1

7 6

7

2

3

4

5

6

1 0

Channel Delay = 1

Last Channel

7

2

3

4

5

6

1 0

Ch 0

2

3

1 0

7

2

3

4

5

6

1 0

Last Channel -1

2

3

4

5

6

1 0

Last Channel -2

7 6

7

2

3

4

5

6

1 0

Channel Delay = 2

Last Channel -1

7

2

3

4

5

6

1 0

Last Channel

2

3

1 0

7

2

3

4

5

6

1 0

Last Channel -2

2

3

4

5

6

1 0

Ch0

7 6

(Default)

Delay = 1

Delay = 2

7

STo

X

STo

X

STo

X

Note: Last Channel = 31, 63, 127 for 2.048 Mb/s, 4.096 Mb/s and 8.192 Mb/s mode respectively

Output Frame Boundary

Note:

X

= 0 to 15

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL50015 | Enhanced 1 K Digital Switch with Stratum 4E DPLL |

| ZL50015GAC | Enhanced 1 K Digital Switch with Stratum 4E DPLL |

| ZL50015QCC | Enhanced 1 K Digital Switch with Stratum 4E DPLL |

| ZL50015QCC1 | Enhanced 1 K Digital Switch with Stratum 4E DPLL |

| ZL50018 | 2 K Digital Switch with Enhanced Stratum 3 DPLL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL50012/GDC | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 256 X 256 3.3V 144LBGA - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC TDM SWITCH 512CH 144LBGA 制造商:Microsemi Corporation 功能描述:IC TDM SWITCH 512CH 144LBGA |

| ZL50012/QCC | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 256 X 256 3.3V 160LQFP - Trays |

| ZL50012_06 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Flexible 512-ch Digital Switch |

| ZL50012GDC | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Flexible 512-ch Digital Switch |

| ZL50012GDG2 | 制造商:Microsemi Corporation 功能描述:Switch Fabric 256 x 256 3.3V 144-Pin LBGA Tray 制造商:Microsemi Corporation 功能描述:TDM SWITCH 512X512 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 256 X 256 3.3V 144LBGA - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC TDM SWITCH 512CH 144LBGA 制造商:Microsemi Corporation 功能描述:IC TDM SWITCH 512CH 144LBGA |

發(fā)布緊急采購,3分鐘左右您將得到回復。