- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373787 > ZL50418GKC (Zarlink Semiconductor Inc.) Managed 16-Port 10/100 M + 2-Port 1 G Ethernet Switch PDF資料下載

參數(shù)資料

| 型號(hào): | ZL50418GKC |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | Managed 16-Port 10/100 M + 2-Port 1 G Ethernet Switch |

| 中文描述: | 管理16端口10/100平方米端口1個(gè)G以太網(wǎng)交換機(jī) |

| 文件頁(yè)數(shù): | 28/163頁(yè) |

| 文件大?。?/td> | 2122K |

| 代理商: | ZL50418GKC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)當(dāng)前第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)

ZL50418

Data Sheet

28

Zarlink Semiconductor Inc.

For example, in the above table a 1 denotes that an outgoing port is eligible to receive a packet from an incoming

port. A 0 (zero) denotes that an outgoing port is not eligible to receive a packet from an incoming port.

In this example:

Data packets received at port #0 are eligible to be sent to outgoing ports 1 and 2.

Data packets received at port #1 are eligible to be sent to outgoing ports 0 and 2.

Data packets received at port #2 are

NOT

eligible to be sent to ports 0 and 1.

5.8.1 Tag-Based VLAN

The ZL50418 supports the IEEE 802.1q specification for “tagging” frames. The specification defines a way to

coordinate VLANs across multiple switches. In the specification, an additional 4-octet header (or “tag”) is inserted in

a frame after the source MAC address and before the frame type. 12 bits of the tag are used to define the VLAN ID.

Packets are then switched through the network with each ZL50418 simply swapping the incoming tag for an

appropriate forwarding tag rather than processing each packet's contents to determine the path. This approach

minimizes the processing needed once the packet enters the tag-switched network. In addition, coordinating VLAN

IDs across multiple switches enables VLANs to extend to multiple switches.

Up to 255 VLANs are supported in the ZL50418. The 4 K VLANs specified in the IEEE 802.1q are mapped to 255

VLAN indexes. The mapping is made by the VLAN index mapping table. Based on the VLAN index (VIXn), the

source and destination port membership is checked against the content in the VLAN Index Port association table. If

the destination port is a member of the VLAN, the packet is forwarded; otherwise it is discarded. If the source port is

not a member, a “New VLAN Port” message is sent to the CPU. A filter can be applied to discard the packet if the

source port is not a member of the VLAN.

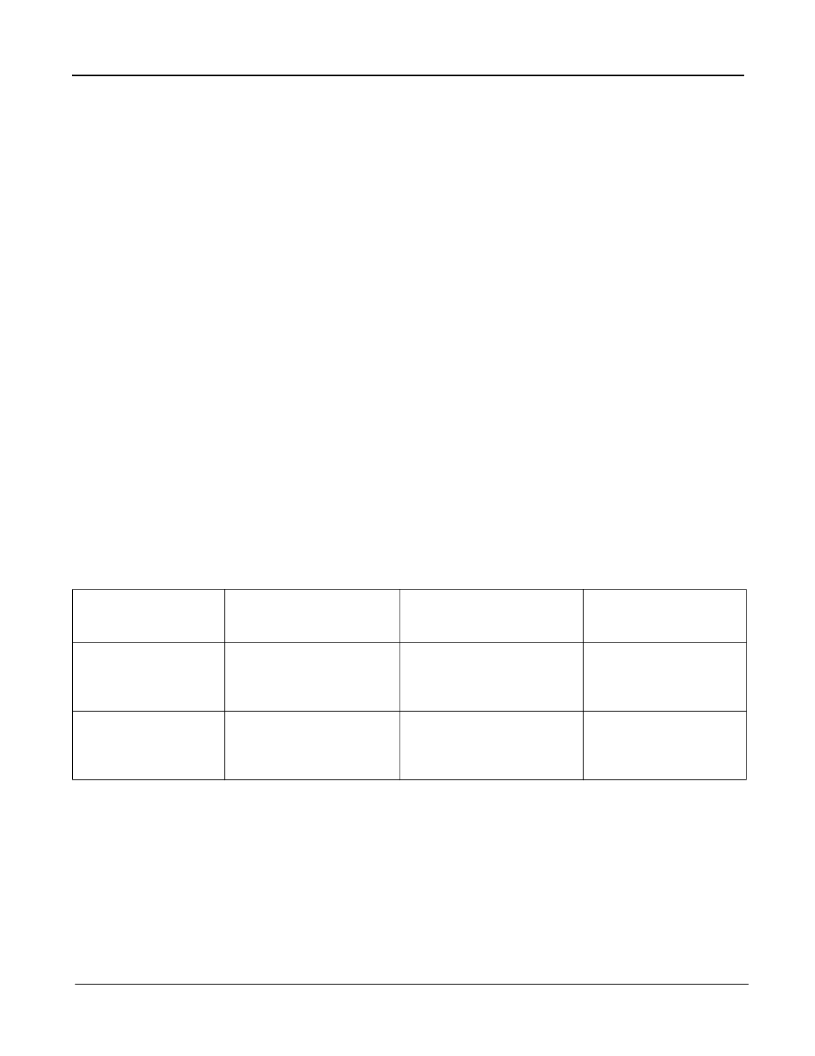

5.9 Memory Configurations

The ZL50418 supports the following memory configurations. Pipeline SBRAM modes support

1 M and 2 M per bank configurations. For detail connection information, please reference the memory application

note.

Configuration

1 M per bank

(Bootstrap pin

TSTOUT7 = open)

2 M per bank

(Bootstrap pin

TSTOUT7 = pull down)

Connections

Single Layer

(Bootstrap pin

TSTOUT13 = open)

Two 128 K x 32

SRAM/bank

or

One 128 K x 64 SRAM/bank

NA

Two 256 K x 32 SRAM/bank

Connect 0E# and WE#

Double Layer

(Bootstrap pin

TSTOUT13 = pull

down)

Four 128 K x 32 SRAM/bank

or

Two 128 K x 64 SRAM/bank

Connect 0E0# and WE0#

Connect 0E1# and WE1#

Table 5 - Supported Memory Configurations (Pipeline SBRAM Mode)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL60101 | 12 x 2.7 Gbps Parallel Fiber Optic Link Transmitter and Receiver |

| ZL60101MJD | 12 x 2.7 Gbps Parallel Fiber Optic Link Transmitter and Receiver |

| ZL60102 | 12 x 2.7 Gbps Parallel Fiber Optic Link Transmitter and Receiver |

| ZL60102MJD | 12 x 2.7 Gbps Parallel Fiber Optic Link Transmitter and Receiver |

| ZL60212 | 880 nm High-Performance Single-chip DUPLEX |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL51B | 制造商:YEASHIN 制造商全稱:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL56B | 制造商:YEASHIN 制造商全稱:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL5V1B | 制造商:YEASHIN 制造商全稱:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL5V6B | 制造商:YEASHIN 制造商全稱:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL60001 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:High speed 2.5 Gbps 850 nm VCSEL |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。