- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371434 > 28F001BX-T (Intel Corp.) 1-MBIT (128K x 8) BOOT BLOCK FLASH MEMORY PDF資料下載

參數(shù)資料

| 型號: | 28F001BX-T |

| 廠商: | Intel Corp. |

| 英文描述: | 1-MBIT (128K x 8) BOOT BLOCK FLASH MEMORY |

| 中文描述: | 1兆位(128K的× 8)引導(dǎo)塊閃存 |

| 文件頁數(shù): | 9/33頁 |

| 文件大小: | 436K |

| 代理商: | 28F001BX-T |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁

28F001BX-T/28F001BX-B

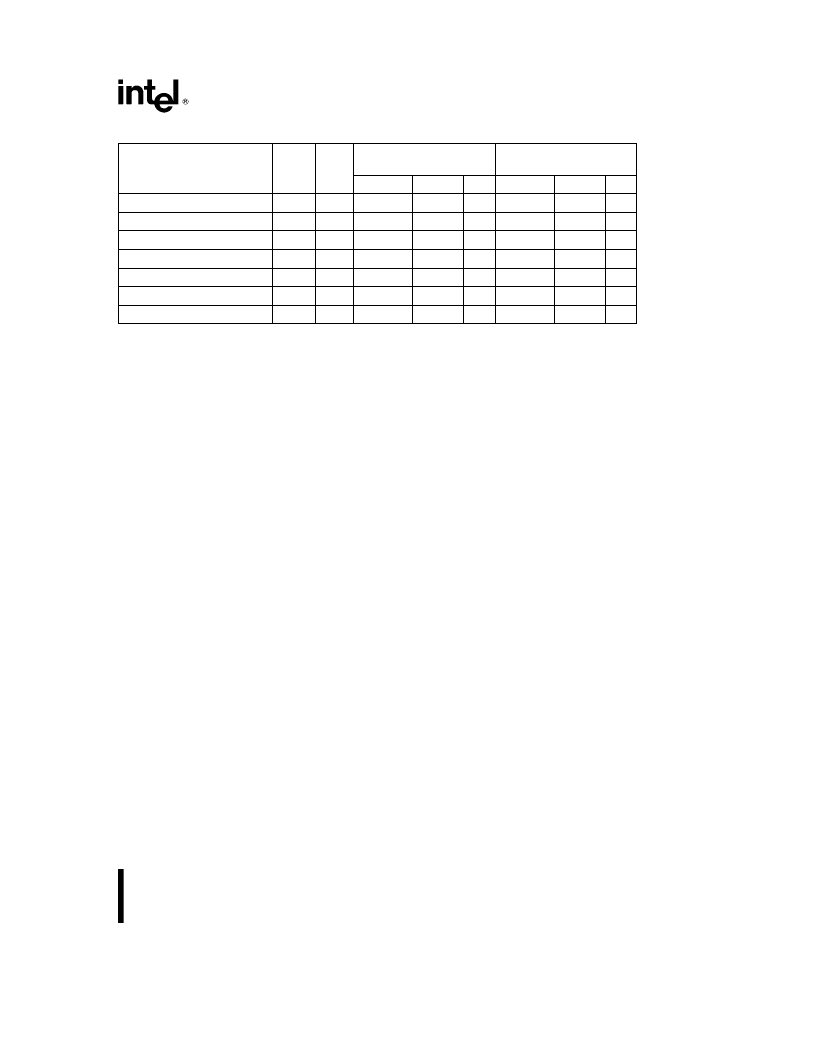

Table 3. 28F001BX Command Definitions

Command

Cycles

Req’d

Bus

Notes

First Bus Cycle

Second Bus Cycle

Operation Address Data Operation Address Data

Read Array/Reset

1

1

Write

X

FFH

Intelligent Identifier

3

2, 3, 4

Write

X

90H

Read

IA

IID

Read Status Register

2

3

Write

X

70H

Read

X

SRD

Clear Status Register

1

Write

X

50H

Erase Setup/Erase Confirm

2

2

Write

BA

20H

Write

BA

D0H

Erase Suspend/Erase Resume

2

Write

X

B0H

Write

X

D0H

Program Setup/Program

2

2, 3

Write

PA

40H

Write

PA

PD

NOTES:

1. Bus operations are defined in Table 2.

2. IA

e

Identifier Address: 00H for manufacturer code, 01H for device code.

BA

e

Address within the block being erased.

PA

e

Address of memory location to be programmed.

3. SRD

e

Data read from Status Register. See Table 4 for a description of the Status Register bits.

PD

e

Data to be programmed at location PA. Data is latched on the rising edge of WE

Y

.

IID

e

Data read from Intelligent Identifiers.

4. Following the Intelligent Identifier command, two read operations access manufacture and device codes.

5. Commands other than those shown above are reserved by Intel for future device implementations and should not be

used.

Read Status Register Command

The 28F001BX contains a Status Register which

may be read to determine when a program or erase

operation is complete, and whether that operation

completed successfully. The Status Register may be

read at any time by writing the Read Status Register

command (70H) to the Command Register. After

writing this command, all subsequent read opera-

tions output data from the Status Register, until an-

other valid command is written to the Command

Register. The contents of the Status Register are

latched on the falling edge of OE

Y

or CE

Y

, which-

ever occurs last in the read cycle. OE

Y

or CE

Y

must be toggled to V

IH

before further reads to up-

date the Status Register latch. The Read Status

Register command functions when V

PP

e

V

PPL

or

V

PPH

.

Clear Status Register Command

The Erase Status and Program Status bits are set to

‘‘1’’ by the Write State Machine and can only be

reset by the Clear Status Register command. These

bits indicate various failure conditions (see Table 4).

By allowing system software to control the resetting

of these bits, several operations may be performed

(such as cumulatively programming several bytes or

erasing multiple blocks in sequence). The Status

Register may then be polled to determine if an error

occurred during that series. This adds flexibility to

the way the device may be used.

Additionally, the V

PP

Status bit (SR.3), when set to

‘‘1’’, MUST be reset by system software before fur-

ther byte programs or block erases are attempted.

To clear the Status Register, the Clear Status Regis-

ter command (50H) is written to the Command Reg-

ister. The Clear Status Register command is func-

tional when V

PP

e

V

PPL

or V

PPH

.

9

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 28F001BX | 5 V Boot Block Flash Memory(5 V引導(dǎo)塊閃速存儲器) |

| 28F002BC | 28F002BC 2-MBIT (256K X 8) BOOT BLOCK FLASH MEMORY |

| 28F002BV-B | 2-MBIT SmartVoltage BOOT BLOCK FLASH MEMORY FAMILY |

| 28F004B3 | 3 Volt Advanced Boot Block Flash Memory(3 V,4M位高級引導(dǎo)塊閃速存儲器) |

| 28F004S3 | BYTE-WIDE SMART 3 FlashFile MEMORY FAMILY 4, 8, AND 16 MBIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 28F001BX-T/28F001BX-B/28F001BN-T/BN-B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:28F001BX-T/28F001BX-B/28F001BN-T/BN-B |

| 28F001BX-T/B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:28F001BX-T/B |

| 28F002BC | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:28F002BC 2-MBIT (256K X 8) BOOT BLOCK FLASH MEMORY |

| 28F002BL-B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2-MBIT (128K x 16. 256K x 8) LOW-POWER BOOT BLOCK FLASH MEMORY FAMILY |

| 28F002BL-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2-MBIT (128K x 16. 256K x 8) LOW-POWER BOOT BLOCK FLASH MEMORY FAMILY |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。