- 您現在的位置:買賣IC網 > PDF目錄298521 > 72V293L6PFG (INTEGRATED DEVICE TECHNOLOGY INC) 64K X 18 OTHER FIFO, 4 ns, PQFP80 PDF資料下載

參數資料

| 型號: | 72V293L6PFG |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | FIFO |

| 英文描述: | 64K X 18 OTHER FIFO, 4 ns, PQFP80 |

| 封裝: | GREEN, PLASTIC, TQFP-80 |

| 文件頁數: | 26/45頁 |

| 文件大小: | 381K |

| 代理商: | 72V293L6PFG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁

32

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V223/233/243/253/263/273/283/293 3.3V HIGH DENSITY SUPERSYNC IITM NARROW BUS FIFO

512 x 18, 1K x 9/18, 2K x 9/18, 4K x 9/18, 8K x 9/18, 16K x 9/18, 32K x 9/18, 64K x 9/18, 128K x 9

FEBRUARY 11, 2009

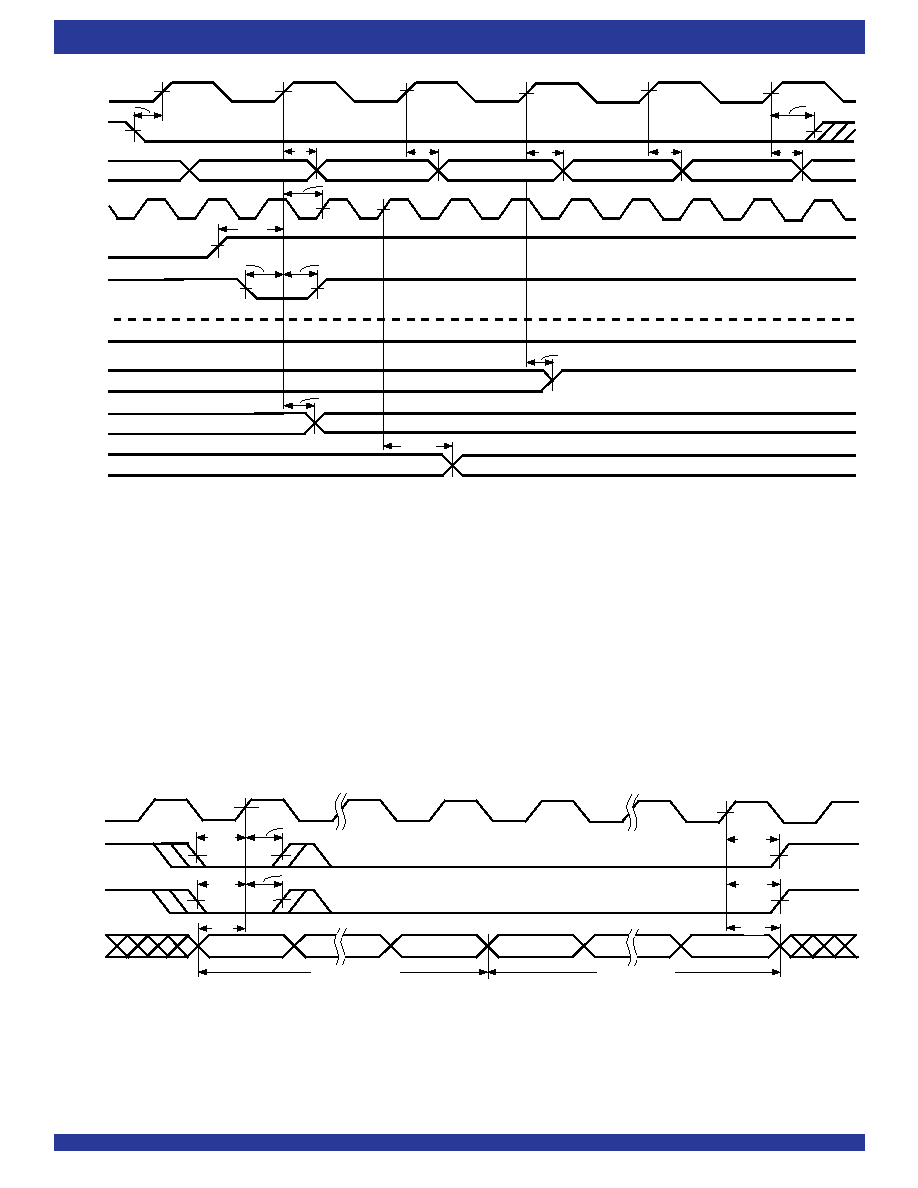

Figure 15. Serial Loading of Programmable Flag Registers (IDT Standard and FWFT Modes)

WCLK

SEN

SI

4666 drw18

tENH

tENS

LD

tDS

BIT 0

EMPTY OFFSET

BIT X(1)

BIT 0

FULL OFFSET

tENH

tLDH

tDH

tLDH

BIT X(1)

tLDS

NOTES:

1. x9 to x9 mode: X = 9 for the IDT72V223, X = 10 for the IDT72V233, X = 11 for the IDT72V243, X = 12 for the IDT72V253, X = 13 for the IDT72V263, X = 14 for the IDT72V273,

X = 15 for the IDT72V283 and X = 16 for the IDT72V293.

2. All other modes: X = 8 for the IDT72V223, X = 9 for the IDT72V233, X = 10 for the IDT72V243, X = 11 for the IDT72V253, X = 12 for the IDT72V263, X = 13 for the IDT72V273,

X = 14 for the IDT72V283 and X = 15 for the IDT72V293.

tA

tRTS

tENH

4666 drw17

tENS

Wx

WCLK

RCLK

REN

RT

OR

PAF

HF

PAE

Q0 - Qn

tSKEW2

12

1

tPAFS

tHF

tPAES

Wx+1

2

W3

WEN

tENS

W2

(3)

4

5

tENH

W4

W5

(3)

3

W1

tA

NOTES:

1. If the part is empty at the point of Retransmit, the output ready flag (

OR), will be updated based on RCLK (Retransmit clock cycle), valid data will also appear on the output.

2. No more than D - 2 words may be written to the FIFO between Reset (Master or Partial) and Retransmit setup. Therefore,

IR will be LOW throughout the Retransmit setup procedure.

If x18 Input or x18 Output bus Width is selected, D = 513 for the IDT72V223, 1,025 for the IDT72V233, 2,049 for the IDT72V243, 4,097 for the IDT72V253, 8,193 for the IDT72V263,

16,385 for the IDT72V273, 32,769 for the IDT72V283 and 65,537 for the IDT72V293.

If both x9 Input and x9 Output bus Widths are selected, D = 1,025 for the IDT72V223, 2,049 for the IDT72V233, 4,097 for the IDT72V243, 8,193 for the IDT72V253, 16,385

for the IDT72V263, 32,769 for the IDT72V273, 65,537 for the IDT72V283 and 131,073 for the IDT72V293.

3.

OE = LOW

4. W1, W2, W3 = first, second and third words written to the FIFO after Master Reset.

5. There must be at least two words written to the FIFO before a Retransmit operation can be invoked.

6. RM is set LOW during

MRS.

Figure 14. Zero Latency Retransmit Timing (FWFT Mode)

相關PDF資料 |

PDF描述 |

|---|---|

| 72V233L6BCG | 1K X 18 OTHER FIFO, 4 ns, PBGA100 |

| 72V3613L20PQF | 64 X 36 OTHER FIFO, 12 ns, PQFP132 |

| 72V3660L6PFG8 | 4K X 36 OTHER FIFO, 4 ns, PQFP128 |

| 7305-0-15-01-47-01-10-0 | BERYLLIUM COPPER, TIN LEAD (300) OVER NICKEL FINISH, PCB TERMINAL |

| 7305-0-15-15-47-27-10-0 | BERYLLIUM COPPER, GOLD (30) OVER NICKEL FINISH, PCB TERMINAL |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 72V293L7-5BC | 功能描述:先進先出 128Kx9/ 64Kx18 3.3V SUPER SYNC II 先進先出 RoHS:否 制造商:IDT 電路數量: 數據總線寬度:18 bit 總線定向:Unidirectional 存儲容量:4 Mbit 定時類型:Synchronous 組織:256 K x 18 最大時鐘頻率:100 MHz 訪問時間:10 ns 電源電壓-最大:3.6 V 電源電壓-最小:6 V 最大工作電流:35 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-80 封裝: |

| 72V293L7-5BCI | 功能描述:先進先出 128Kx9/ 64Kx18 3.3V SUPER SYNC II 先進先出 RoHS:否 制造商:IDT 電路數量: 數據總線寬度:18 bit 總線定向:Unidirectional 存儲容量:4 Mbit 定時類型:Synchronous 組織:256 K x 18 最大時鐘頻率:100 MHz 訪問時間:10 ns 電源電壓-最大:3.6 V 電源電壓-最小:6 V 最大工作電流:35 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-80 封裝: |

| 72V293L7-5PF | 功能描述:先進先出 128Kx9/ 64Kx18 3.3V SUPER SYNC II 先進先出 RoHS:否 制造商:IDT 電路數量: 數據總線寬度:18 bit 總線定向:Unidirectional 存儲容量:4 Mbit 定時類型:Synchronous 組織:256 K x 18 最大時鐘頻率:100 MHz 訪問時間:10 ns 電源電壓-最大:3.6 V 電源電壓-最小:6 V 最大工作電流:35 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-80 封裝: |

| 72V293L7-5PF8 | 功能描述:先進先出 128Kx9/ 64Kx18 3.3V SUPER SYNC II 先進先出 RoHS:否 制造商:IDT 電路數量: 數據總線寬度:18 bit 總線定向:Unidirectional 存儲容量:4 Mbit 定時類型:Synchronous 組織:256 K x 18 最大時鐘頻率:100 MHz 訪問時間:10 ns 電源電壓-最大:3.6 V 電源電壓-最小:6 V 最大工作電流:35 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-80 封裝: |

| 72V293L7-5PF9 | 制造商:Integrated Device Technology Inc 功能描述:FIFO Mem Sync Dual Depth/Width Uni-Dir 64K x 18/128K x 9 80-Pin TQFP |

發(fā)布緊急采購,3分鐘左右您將得到回復。