- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378211 > 80960JS (Intel Corp.) High Performance 32-bit Embedded 3.3V Microprocessor(3.3V高性能32位嵌入式處理器) PDF資料下載

參數(shù)資料

| 型號(hào): | 80960JS |

| 廠商: | Intel Corp. |

| 英文描述: | High Performance 32-bit Embedded 3.3V Microprocessor(3.3V高性能32位嵌入式處理器) |

| 中文描述: | 高性能32位嵌入式微處理器3.3(3.3高性能32位嵌入式處理器) |

| 文件頁(yè)數(shù): | 20/86頁(yè) |

| 文件大小: | 1257K |

| 代理商: | 80960JS |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)

80960JA/JF/JD/JS/JC/JT 3.3 V Microprocessor

20

Datasheet

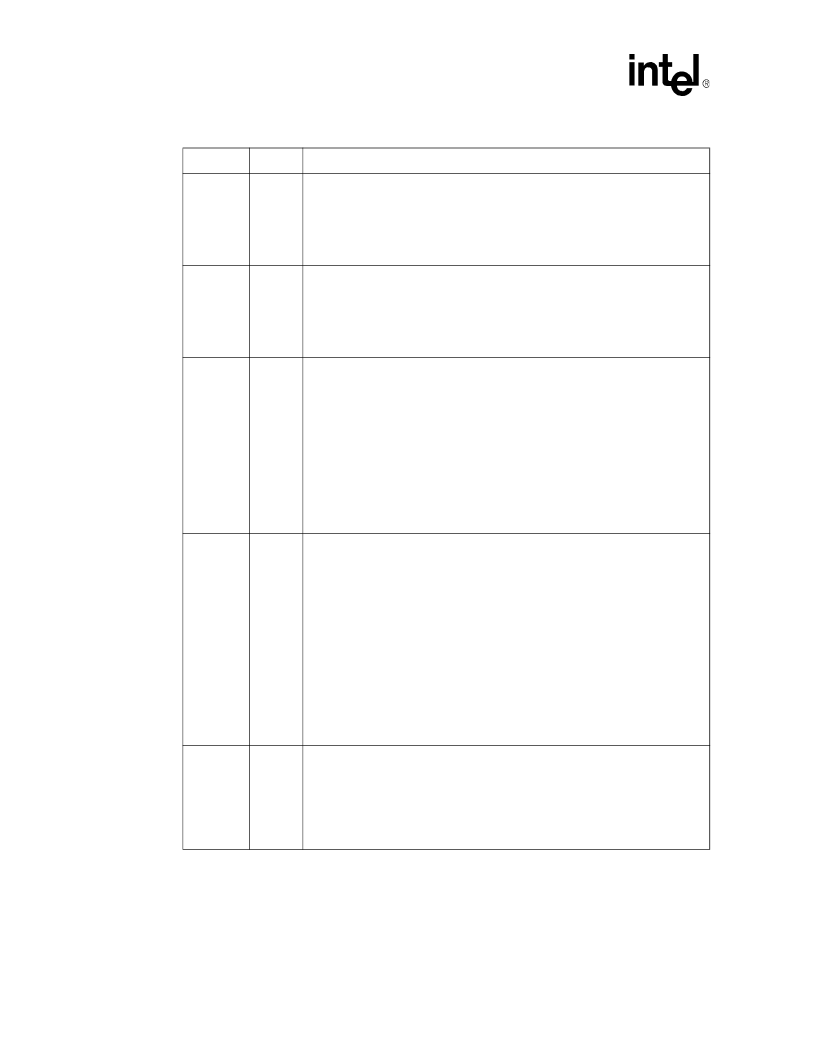

DEN#

O

R(1)

H(Z)

P(1)

DATA ENABLE

indicates data transfer cycles during a bus access. DEN# is

asserted at the start of the first data cycle in a bus access and deasserted at the end

of the last data cycle. DEN# is used with DT/R# to provide control for data

transceivers connected to the data bus.

0 = data cycle

1 = not data cycle

BLAST#

O

R(1)

H(Z)

P(1)

BURST LAST

indicates the last transfer in a bus access. BLAST# is asserted in the

last data transfer of burst and non-burst accesses. BLAST# remains active as long

as wait states are inserted via the RDYRCV# pin. BLAST# becomes inactive after

the final data transfer in a bus cycle.

0 = last data transfer

1 = not last data transfer

RDYRCV#

I

S(L)

READY/RECOVER

indicates that data on AD lines can be sampled or removed. If

RDYRCV# is not asserted during a T

d

cycle, the T

d

cycle is extended to the next

cycle by inserting a wait state (T

w

).

0 = sample data

1 = don

’

t sample data

The RDYRCV# pin has another function during the recovery (T

r

) state. The

processor continues to insert additional recovery states until it samples the pin

HIGH. This function gives slow external devices more time to float their buffers

before the processor begins to drive address again.

0 = insert wait states

1 = recovery complete

LOCK#/

ONCE#

I/O

S(L)

R(H)

H(Z)

P(1)

BUS LOCK

indicates that an atomic read-modify-write operation is in progress. The

LOCK# output is asserted in the first clock of an atomic operation and deasserted in

the last data transfer of the sequence. The processor does not grant HOLDA while it

is asserting LOCK#. This prevents external agents from accessing memory involved

in semaphore operations.

0 = Atomic read-modify-write in progress

1 = Atomic read-modify-write not in progress

ONCE MODE:

The processor samples the ONCE# input during reset. If it is

asserted LOW at the end of reset, the processor enters ONCE mode. In ONCE

mode, the processor stops all clocks and floats all output pins. The pin has a weak

internal pullup which is active during reset to ensure normal operation when the pin

is left unconnected.

0 = ONCE mode enabled

1 = ONCE mode not enabled

HOLD

I

S(L)

HOLD

: A request from an external bus master to acquire the bus. When the

processor receives HOLD and grants bus control to another master, it asserts

HOLDA, floats the address/data and control lines and enters the T

h

state. When

HOLD is deasserted, the processor deasserts HOLDA and enters either the T

i

or

T

a

state, resuming control of the address/data and control lines.

0 = no hold request

1 = hold request

Table 8. Pin Description

—

External Bus Signals (Sheet 3 of 4)

NAME

TYPE

DESCRIPTION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 80960JC | High Performance 32-Bit Embedded 3.3V Microprocessor(3.3V高性能32位嵌入式處理器) |

| 80960KB | Embedded 32-Bit Microprocessor With Integrated Floating-Point Unit(帶有集成的浮點(diǎn)單元的嵌入式32位微處理器) |

| 80960MC | Embedded 32Bit Microprocessor With Integrated Floating_Point Unit And Memory Unit(帶有集成的浮點(diǎn)單元和存儲(chǔ)器管理單元的嵌入式32位微處理器) |

| 80960RM | 80960RM I/O Processor(80960RM I/O 處理器) |

| 80960RN | 80960RN I/O Processor(80960RN I/O 處理器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 80960JT | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:3.3 V EMBEDDED 32-BIT MICROPROCESSOR |

| 80960KA | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:EMBEDDED 32-BIT MICROPROCESSOR |

| 80960KB | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:EMBEDDED 32-BIT MICROPROCESSOR WITH INTEGRATED FLOATING-POINT UNIT |

| 80960MC | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:EMBEDDED 32-BIT MICROPROCESSOR WITH INTEGRATED FLOATING-POINT UNIT AND MEMORY MANAGEMENT UNIT |

| 80960SA | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:EMBEDDED 32-BIT MICROPROCESSOR WITH 16-BIT BURST DATA BUS |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。