- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄378217 > 82845GV (INTEL CORP) Intel 82845G/82845GL/82845GV Graphics and Memory Controller Hub (GMCH) PDF資料下載

參數(shù)資料

| 型號(hào): | 82845GV |

| 廠商: | INTEL CORP |

| 元件分類: | 外設(shè)及接口 |

| 英文描述: | Intel 82845G/82845GL/82845GV Graphics and Memory Controller Hub (GMCH) |

| 中文描述: | MULTIFUNCTION PERIPHERAL, PBGA760 |

| 封裝: | 37.50 X 37.50 MM, 1 MM PITCH, FLIP CHIP, BGA-760 |

| 文件頁(yè)數(shù): | 36/193頁(yè) |

| 文件大小: | 2990K |

| 代理商: | 82845GV |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)當(dāng)前第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)

Signal Description

36

Intel

82845G/82845GL/82845GV GMCH Datasheet

2.7

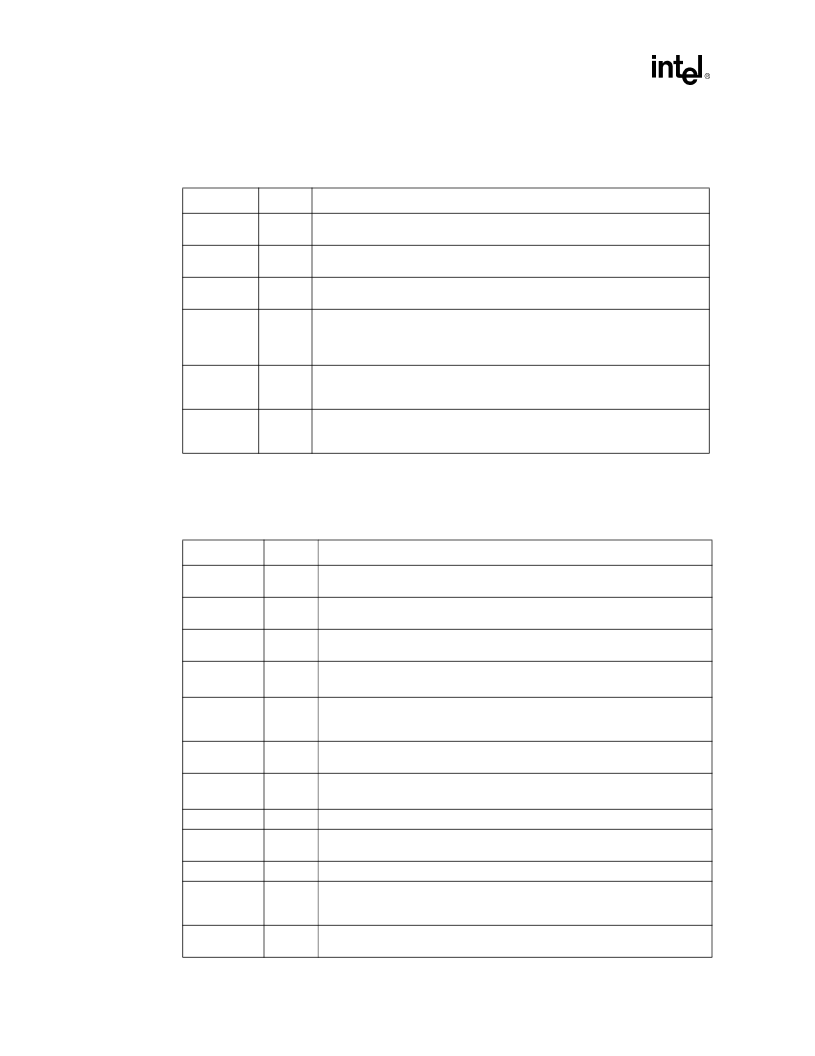

Clocks, Reset, and Miscellaneous Signals

2.8

RCOMP, VREF, VSWING Signals

Signal Name

Type

Description

HCLKP

HCLKN

I

CMOS

Differential Host Clock In:

These pins receive a low voltage differential host clock

from the external clock synthesizer.

GCLKIN

I

LVTTL

66 MHz Clock In:

This pin receives a 66 MHz clock from the clock synthesizer.

This clock is used by AGP and hub interface clock domains.

DREFCLK

I

LVTTL

Display Clock Input:

This pin provides a 48 MHz input clock to the Display PLL

that is used for 2D/Video/Flat Panel and DAC.

RSTIN#

I

LVTTL

Reset In:

When asserted, this signal asynchronously resets the GMCH logic. This

signal is connected to the PCIRST# output of the Intel

ICH4. All AGP/PCI output

and bi-directional signals will also tri-state compliant to

PCI Local Bus

Specification, Revision 2.0

and

PCI Local Bus Specification, Revision 2.1

.

PWROK

I

3.3 V

GPIO

Power OK:

When asserted, PWROK is an indication to the GMCH that the core

power and GCLKIN have been stable for at least 10 μs.

TESTIN#

I

1.5 V

CMOS

Test Input:

This pin is used for manufacturing and board lever test purposes.

Signal Name

Type

Description

HDVREF_[2:0]

I

Host Data Reference Voltage:

Reference voltage input for the data signals of the

Host AGTL+ interface.

HA_VREF

I

Host Address Reference Voltage:

Reference voltage input for the address

signals of the Host AGTL+ interface.

HCC_VREF

I

Host Common Clock Reference Voltage:

Reference voltage input for the

common clock signals of the Host AGTL+ interface.

HX_RCOMP

HY_RCOMP

I/O

CMOS

Host RCOMP:

These pins are used to calibrate the Host AGTL+ I/O buffers.

HX_SWING

HY_SWING

I

Host Voltage Swing:

These pins provide a reference voltage used by the PSB

RCOMP circuit. HX_SWING is used for the signals handled by HX_RCOMP, and

HY_SWING is used for the signals handled by HY_RCOMP.

SM_VREF

I

Memory Reference Voltage:

Reference voltage input for DQ, DQS &

SRCVEN_IN#.

SMXRCOMP

SMYRCOMP

I/O

CMOS

Memory RCOMP:

These pins are used to calibrate the memory I/O buffers.

AGP_VREF

I

AGP Reference:

The reference voltage for the AGP/DVO I/O buffers is 0.75 V.

AGP_RCOMP

I/O

CMOS

Compensation for AGP:

This signal is used to calibrate the AGP/DVO buffers.

This signal should be connected to ground through a 40

pull-down resistor.

HI_VREF

I

HI Reference:

Reference voltage input for the hub interface.

HI_RCOMP

I/O

CMOS

Compensation for HI:

This signal is used to calibrate the hub interface I/O

buffers. This signal should be connected to 1.5 V through a 68.1

1% pull-up

resistor

HI_SWING

I

HI Voltage Swing:

This signal provides a reference voltage used by the

HI_RCOMP circuit.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 82845Gx | Intel 82845G/82845GL/82845GV Graphics and Memory Controller Hub (GMCH) |

| 82845MP | Intel 845 Family Chipset-Mobile 82845MP/82845MZ Chipset Memory Controller Hub Mobile (MCH-M) |

| 82845Mx | Intel 845 Family Chipset-Mobile 82845MP/82845MZ Chipset Memory Controller Hub Mobile (MCH-M) |

| 82845MZ | Intel 845 Family Chipset-Mobile 82845MP/82845MZ Chipset Memory Controller Hub Mobile (MCH-M) |

| 82845PE | 82845GE Graphics and Memory Controller Hub (GMCH) and 82845PE Memory Controller Hub (MCH) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 82845GX | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel 82845G/82845GL/82845GV Graphics and Memory Controller Hub (GMCH) |

| 82845MP | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel 845 Family Chipset-Mobile 82845MP/82845MZ Chipset Memory Controller Hub Mobile (MCH-M) |

| 82845MX | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel 845 Family Chipset-Mobile 82845MP/82845MZ Chipset Memory Controller Hub Mobile (MCH-M) |

| 82845MZ | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel 845 Family Chipset-Mobile 82845MP/82845MZ Chipset Memory Controller Hub Mobile (MCH-M) |

| 82845PE | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:82845GE Graphics and Memory Controller Hub (GMCH) and 82845PE Memory Controller Hub (MCH) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。