- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366550 > AM79C940VCW (ADVANCED MICRO DEVICES INC) Media Access Controller for Ethernet (MACE) PDF資料下載

參數(shù)資料

| 型號(hào): | AM79C940VCW |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Media Access Controller for Ethernet (MACE) |

| 中文描述: | 4 CHANNEL(S), 10M bps, LOCAL AREA NETWORK CONTROLLER, PQFP80 |

| 封裝: | TQFP-80 |

| 文件頁(yè)數(shù): | 54/122頁(yè) |

| 文件大?。?/td> | 914K |

| 代理商: | AM79C940VCW |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)當(dāng)前第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)

AMD

54

Am79C940

Receive frames which have a length field of 46 bytes or

greater will be passed to the host unmodified.

Since any valid Ethernet Type field value will always be

greater than a normal 802.3 Length field, the MACE de-

vice will not attempt to strip valid Ethernet frames.

Note that for some network protocols, the value passed

in the Ethernet Type and/or 802.3 Length field is not

compliant with either standard and may cause

problems.

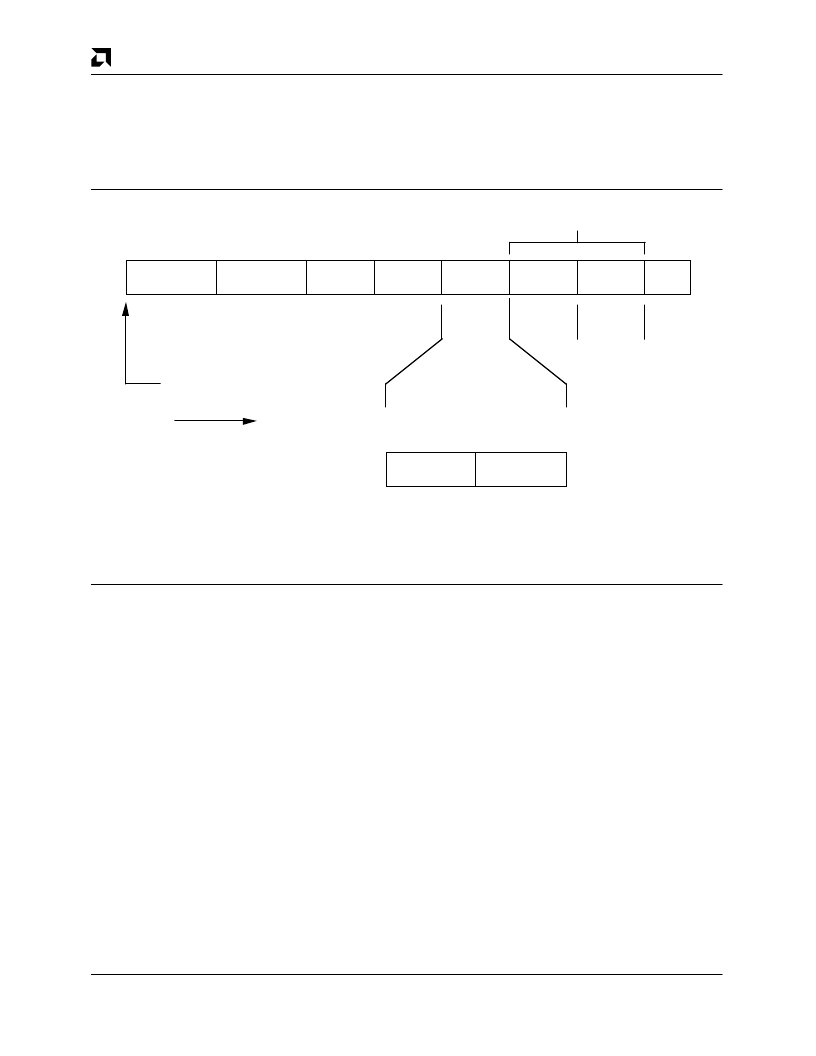

The diagram below shows the byte/bit ordering of the re-

ceived length field for an 802.3 compatible frame format.

16907A-013A

Preamble

1010....1010

SYNCH

10101011

Dest.

ADDR.

SRCE.

ADDR.

Length

LLC

DATA

Pad

FCS

56

Bits

8

Bits

6

Bytes

6

Bytes

2

Bytes

46-1500

Bytes

4

Bytes

Most

Significant

Byte

Least

Significant

Byte

Bit

0

Bit

7

Start of Packet

at Time= 0

Increasing Time

Bit

7

Bit

0

45-0

Bytes

1-1500

Bytes

16235C-9

802.3 Packet and Length Field Transmission Order

Receive FCS Checking

Reception and checking of the received FCS is per-

formed automatically by the MACE device. Note that if

the Automatic Pad Stripping feature is enabled, the re-

ceived FCS will be verified against the value computed

for the incoming bit stream including pad characters, but

it will not be passed through the Receive FIFO to the

host. If an FCS error is detected, this will be reported by

the FCS bit (bit 4) in the Receive Frame Status.

Receive Status Information

The

EOF

indication signals that the last byte/word of

data has been passed from the FIFO for the specific

frame. This will be accompanied by a RCVINT indication

in the the Interrupt Register signaling that the Receive

Frame Status has been updated, and must be read. The

Receive Frame Status is a single location which must be

read four times to allow the four bytes of status informa-

tion associated with each frame to be read. Further data

read operations from the Receive FIFO using the Regis-

ter Address mode, will be ignored by the MACE device

(indicated by the MACE chip not returning

DTV

) until all

four bytes of the Receive Frame Status have been read.

Alternatively, the FIFO Direct access mode may be

used to read the Receive Frame Status through the Re-

ceive FIFO. In either case, the 4-byte total must be read

before additional receive data can be read from the Re-

ceive FIFO. However, the

RDTREQ

indication will con-

tinue to reflect the state of the Receive FIFO as normal,

regardless of whether the Receive Frame Status has

been read.

DTV

will not be returned when a read opera-

tion is performed on the Receive Frame Status location

and no valid status is present or ready.

Note that the Receive Frame Status can be read using

either the Register Address or FIFO Direct modes. For

additional details, see the section Receive FIFO Read.

Receive Exception Conditions

Exception conditions for frame reception fall into two

distinct categories; those which are the result of normal

network operation, and those which occur due to abnor-

mal network and/or host related events.

Normal events which may occur and which are handled

autonomously by the MACE device are basically colli-

sions within the slot time and automatic runt packet de-

letion. The MACE device will ensure that any receive

packet which experiences a collision within 512 bit times

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C940 | Media Access Controller for Ethernet (MACE) |

| AM79C940JCW | Media Access Controller for Ethernet (MACE) |

| AM79C940KCW | Media Access Controller for Ethernet (MACE) |

| AM79C960 | PCnetTM-ISA Single-Chip Ethernet Controller |

| AM79C960KC | PCnetTM-ISA Single-Chip Ethernet Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C940VI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN Node Controller |

| AM79C940VI/W | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN Node Controller |

| AM79C945 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| AM79C945-16 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| AM79C945-16JC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN Node Controller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。