- 您現在的位置:買賣IC網 > PDF目錄366550 > AM79C960KC (ADVANCED MICRO DEVICES INC) PCnetTM-ISA Single-Chip Ethernet Controller PDF資料下載

參數資料

| 型號: | AM79C960KC |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | PCnetTM-ISA Single-Chip Ethernet Controller |

| 中文描述: | 2 CHANNEL(S), 10M bps, LOCAL AREA NETWORK CONTROLLER, PQFP120 |

| 封裝: | CARRIER RING, PLASTIC, QFP-120 |

| 文件頁數: | 74/127頁 |

| 文件大小: | 814K |

| 代理商: | AM79C960KC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁當前第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁

P R E L I M I N A R Y

AMD

1-416

Am79C960

15-5

RES

Reserved locations. Written as

zero and read as undefined.

This mode places the PCnet-ISA

controller in the GPSI Mode. This

mode will reconfigure the Exter-

nal Address Pins so that the

GPSI port is exposed. This al-

lows bypassing the MENDEC-

TMAU logic. This bit should only

be set if the external logic sup-

ports GPSI operation. Damage

to the device may occur in a non-

GPSI configuration. Refer to the

GPSI section.

Runt Packet Accept. This bit

forces the CORE receive logic to

accept Runt Packets. This bit al-

lows for faster testing.

For test purposes only. Reserved

locations. Written as zero and

read as undefined.

4

GPSIEN

3

RPA

2-0

RES

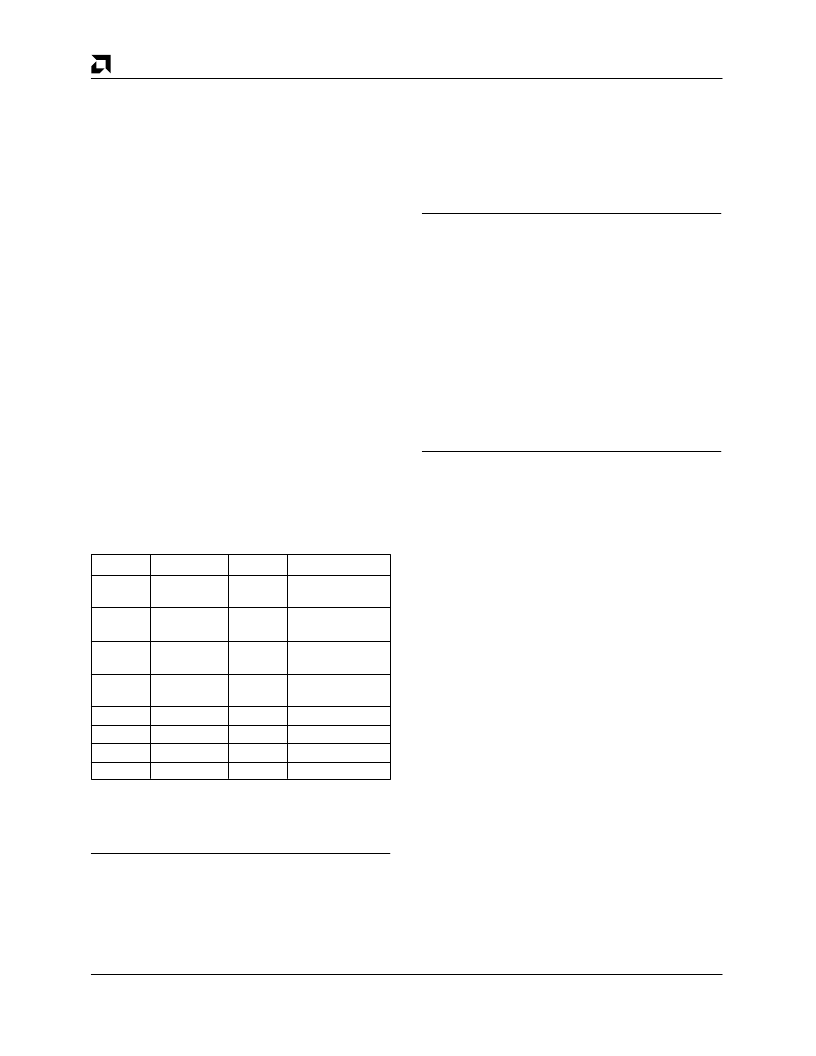

ISA Bus Configuration Registers

The ISA Bus Data Port (IDP) allows access to registers

which are associated with the ISA bus. These registers

are called ISA Bus Configuration Registers (ISACSRs),

and are indexed by the value in the Register Address

Port (RAP). The table below defines the ISACSRs which

can be accessed. All registers are 16 bits. The “Default”

value is the value in the register after reset and is

hexadecimal.

ISACSR

0

1

2

3

MNEMONIC

MSRDA

Default

0005H

Name

Master Mode

Read Active

Master Mode

Write Active

Miscellaneous

Configuration

Reserved for

future AMD use

Link Integrity

Default: RCV

Default: RCVPOL

Default: XMT

MSWRA

0005H

MC

0002H

Reserved

N/A

4

5

6

7

LED0

LED1

LED2

LED3

0000H

0084H

0008H

0090H

ISACSR0: Master Mode Read Active

Bit

Name

Description

15-4

RES

Reserved locations. Written as

zero and read as undefined.

This register is used to tune the

MEMR

command signal active

time. The value stored in MSRDA

defines the number of 50 ns peri-

ods that the command signal is

3-0

MSRDA

active. The default value of 5h in-

dicates 250 ns pulse widths. A

value of 0 or 1 will generate 50 ns

wide commands.

ISACSR1: Master Mode Write Active

Bit

Name

Description

15-4

RES

Reserved locations. Written as

zero and read as undefined.

This register is used to tune the

MEMW

command signal active

time. The value stored in

MSWRA defines the number of

50 ns periods that the command

signal is active. The default value

of 5h indicates 250 ns pulse

widths. A value of 0 or 1 will gen-

erate 50 ns wide commands.

3-0

MSWRA

ISACSR2: Miscellaneous Configuration

Bit

Name

Description

15 MODE_STATUS Mode Status. This is a read-only

register which indicates whether

the PCnet-ISA is configured in

shared memory mode. A set

condition

memory while a clear condition

indicates bus-master condition.

14-8

RES

Reserved locations. Written and

read as zero.

7

EISA_LVL

EISA_LVL allows for EISA level-

sensitive

EISA_LVL is cleared when

RESET is asserted. When

EISA_LVL is a zero, the IRQ pin

is configured for ISA edge sensi-

tive full CMOS driver. When

EISA_LVL is set by writing a one,

the IRQ pin is configured as an

EISA level-sensitive interrupt

open

EISA_LVL is set to one, the IRQ

pin assertion level is active low.

6-5

RES

Reserved locations. Written and

read as zero.

4

ISAINACT

ISAINACT allows for reduced in-

active timing appropriate for

modern

ISAINACT is cleared when

RESET is asserted. When

ISAINACT is a zero, tMMR3 and

tMMW3 parameters are nomi-

nally 200 ns, which is com-

patible with EISA system. When

ISAINACT is set by writing a one,

indicates

shared-

interrupt

support.

drain

output.

When

ISA

machines.

相關PDF資料 |

PDF描述 |

|---|---|

| AM79C960KCW | PCnetTM-ISA Single-Chip Ethernet Controller |

| AM79C961AKCW | PCnet ⑩-ISA II Jumperless, Full Duplex Single-Chip Ethernet Controller for ISA |

| AM79C961AKC | PCnet ⑩-ISA II Jumperless, Full Duplex Single-Chip Ethernet Controller for ISA |

| AM79C961A | PCnet ⑩-ISA II Jumperless, Full Duplex Single-Chip Ethernet Controller for ISA |

| AM79C961AKIW | PCnet⑩-ISA II Jumperless, Full Duplex Single-Chip Ethernet Controller for ISA |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AM79C960KC/W | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN Node Controller |

| AM79C960KCW | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnetTM-ISA Single-Chip Ethernet Controller |

| AM79C961 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Am79C961 - PCnet-ISA+ Jumperless Single-Chip Ethernet Controller for ISA |

| AM79C961/AM79C961A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Using the Am79C961/Am79C961A (PCnet-ISA+/PCnet-ISA II) Survival Guide? 134KB (PDF) |

發(fā)布緊急采購,3分鐘左右您將得到回復。