- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366550 > AM79C961AVIW (ADVANCED MICRO DEVICES INC) PCnet⑩-ISA II Jumperless, Full Duplex Single-Chip Ethernet Controller for ISA PDF資料下載

參數(shù)資料

| 型號(hào): | AM79C961AVIW |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | PCnet⑩-ISA II Jumperless, Full Duplex Single-Chip Ethernet Controller for ISA |

| 中文描述: | 2 CHANNEL(S), 10M bps, LOCAL AREA NETWORK CONTROLLER, PQFP144 |

| 封裝: | TQFP-144 |

| 文件頁數(shù): | 83/206頁 |

| 文件大小: | 1507K |

| 代理商: | AM79C961AVIW |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁當(dāng)前第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁

Am79C961A

83

there are link beat pulses or valid frames present. This

LED0 pin can be used to drive a LED and/or external

hardware that directly controls the SLEEP pin of the

PCnet-ISA II controller. This configuration effectively

wakes the system when there is any activity on the

10BASE-T link.

Access Operations (Software)

We begin by describing how byte and word data are

addressed on the ISA bus, including conversion cycles

where 16-bit accesses are turned into 8-bit accesses

because the resource accessed did not support 16-bit

operations. Then we describe how registers and other

resources are accessed. This section is for the device

programmer, while the next section (bus cycles) is for

the hardware designer.

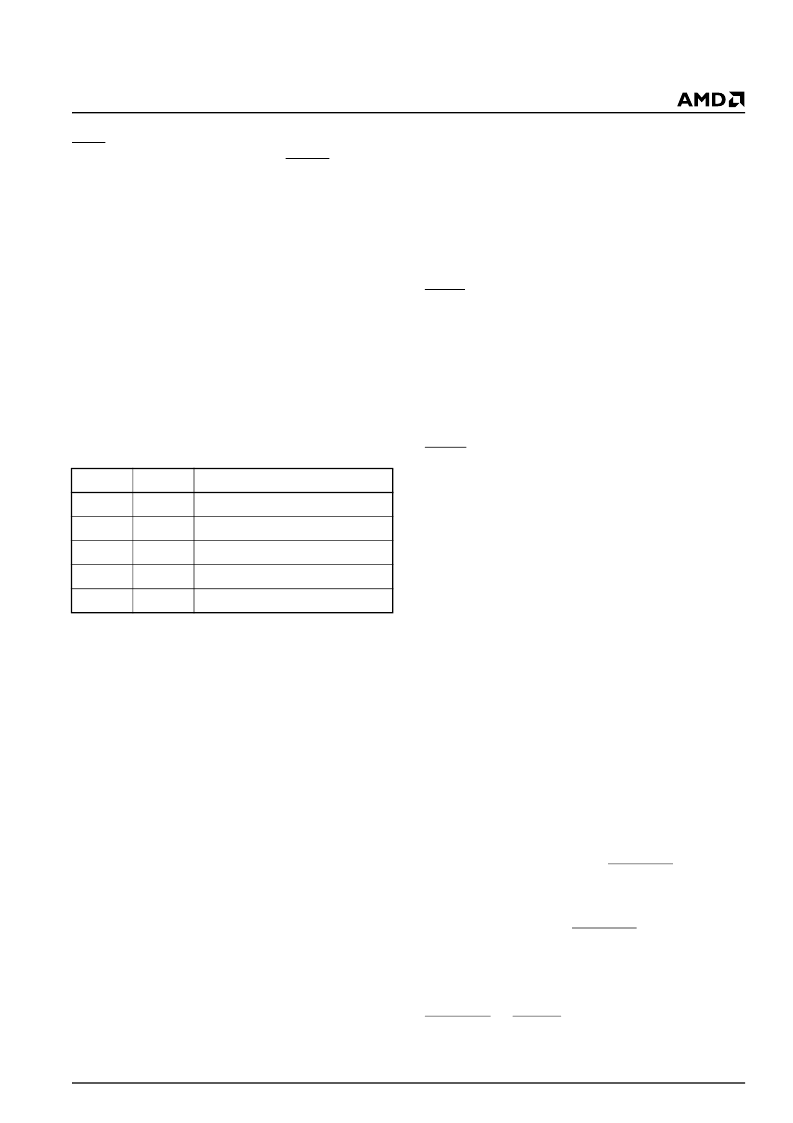

I/O Resources

The PCnet-ISA II controller has both I/O and memory

resources. In the I/O space the resources are orga-

nized as indicated in the following table:

The PCnet-ISA II controller does not respond to any

addresses outside of the offset range 0-17h. I/O offsets

18h and up are not used by the PCnet-ISA II controller.

I/O Register Access

The register address port (RAP) is shared by the regis-

ter data port (RDP) and the ISACSR data port (IDP) to

save registers. To access the Ethernet controller

’

s RDP

or IDP, the RAP should be written first, followed by the

read or write access to the RDP or IDP. I/O register

accesses should be coded as 16-bit accesses, even if

the PCnet-ISA II controller is hardware configured for

8-bit I/O bus cycles. It is acceptable (and transparent)

for the motherboard to turn a 16-bit software access

into two separate 8-bit hardware bus cycles. The moth-

erboard accesses the low byte before the high byte and

the PCnet-ISA II controller has circuitry to specifically

support this type of access.

The reset register causes a reset when read. Any value

will be accepted and the cycle may be 8 or 16 bits wide.

Writes are ignored.

All PCnet-ISA II controller register accesses should be

coded as 16-bit operations.

“

Note that the RAP is cleared on Reset.

”

IEEE Address Access

The address PROM may be an external memory

device that contains the node

’

s unique physical Ether-

net address and any other data stored by the board

manufacturer. The software accesses must be 16-bit.

This information may be stored in the EEPROM.

Boot PROM Access

The boot PROM is an external memory resource

located by the address selected by the EEPROM or the

BPAM input in

slave

mode. It may be software

accessed as an 8-bit or 16-bit resource but the latter is

recommended for best performance.

Static RAM Access

The static RAM is only present in the Bus Slave mode.

In the Bus Slave mode, two SRAM access schemes

are available. When the Shared Memory architecture

mode is selected, the SRAM is accessed using ISA

memory cycles to the address range selected by the

SMAM input. It may be accessed as an 8 or 16-bit

resource but the latter is recommended for best perfor-

mance. When the Programmed I/O architecture mode

is selected, the SRAM is accessed through ISACSR0

and ISACSR1 using the RAP and IDP.

Bus Cycles (Hardware)

The PCnet-ISA II controller supports both 8-bit and

16-bit hardware bus cycles. The following sections out-

line where any limitations apply based upon the archi-

tecture mode and/or the resource that is being

accessed (PCnet-ISA II controller registers, address

PROM, boot PROM, or shared memory SRAM). For

completeness, the following sections are arranged by

architecture (Bus Master Mode or Bus Slave Mode).

SRAM resources apply only to Bus Slave Mode.

All resources (registers, PROMs, SRAM) are pre-

sented to the ISA bus by the PCnet-ISA II controller.

With few exceptions, these resources can be config-

ured for either 8-bit or 16-bit bus cycles. The I/O

resources (registers, address PROM) are width con-

figured using the EEPROM. The memory resources

(boot PROM, SRAM) are width configured by external

hardware.

For 16-bit memory accesses, hardware external to the

PCnet-ISA II controller asserts MEMCS16 when either

of the two memory resources is selected. The ISA bus

requires that all memory resources within a block of

128 Kbytes be the same width, either 8- or 16-bits. The

reason for this is that the MEMCS16 signal is generally

a decode of the LA

17-23

address lines. 16-bit memory

capability is desirable since two 8-bit accesses take the

same amount of time as four 16-bit accesses.

All accesses to 8-bit resources (which do not return

MEMCS16 or IOCS16) use SD0-7. If an odd byte is

accessed, the Current Master swap buffer turns on.

Offset

#Bytes

Register

0h

16

IEEE Address

10h

2

RDP

12h

2

RAP(shared by RDP and IDP)

14h

2

Reset

16h

2

IDP

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| Am79C965A | PCnet?-32 Single-Chip 32-Bit Ethernet Controller |

| AM79C970AKCW | PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

| AM79C970AKC | PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

| AM79C970A | PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

| AM79C970AVCW | PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C961AWW WAF | 制造商:Advanced Micro Devices 功能描述: |

| AM79C961KC | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnetTM-ISA+ Jumperless Single-Chip Ethernet Controller for ISA |

| AM79C961KC/W | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnetTM-ISA+ Jumperless Single-Chip Ethernet Controller for ISA |

| AM79C965A | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet?-32 Single-Chip 32-Bit Ethernet Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。