- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄378406 > ARM610 (Zarlink Semiconductor Inc.) General purpose 32-bit microprocessor PDF資料下載

參數(shù)資料

| 型號(hào): | ARM610 |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | General purpose 32-bit microprocessor |

| 中文描述: | 通用32位微處理器 |

| 文件頁(yè)數(shù): | 14/173頁(yè) |

| 文件大?。?/td> | 897K |

| 代理商: | ARM610 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)

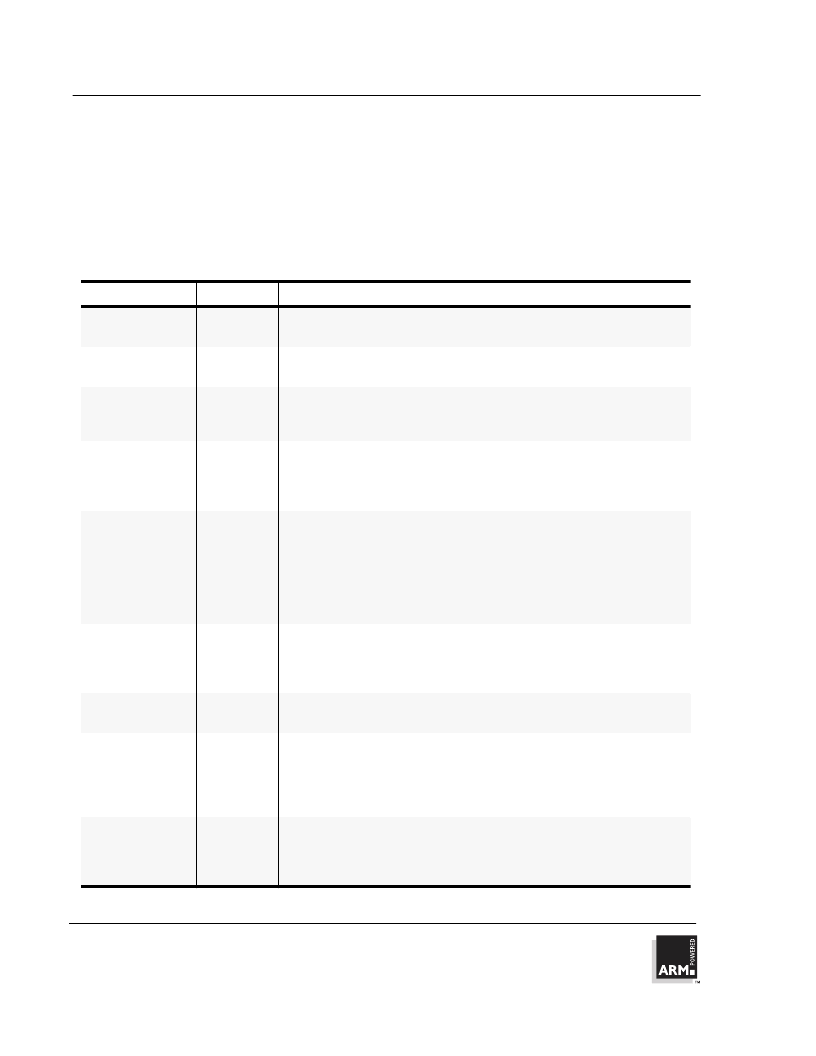

Signal Description

ARM610 Data Sheet

2-2

2.1

Signal Description

Key to Signal Types

IT

Input, TTL threshold

OCZ

Output, CMOS levels, tristateable

ITOTZ

Input/output tristateable, TTL thresholds

ICK

Input, clock levels

Name

Type

Description

A[31:0]

OCZ

Address Bus. This bus signals the address requested for memory

accesses. Normally it changes during

MCLK

HIGH.

ABE

IT

Address bus enable. When this input is LOW, the address bus

nRW

,

nBW

and

LOCK

are put into a high impedance state (Note 1).

A[31:0]

,

ABORT

IT

External abort. Allows the memory system to tell the processor that a

requested access has failed. Only monitored when

external memory.

ARM610

is accessing

ALE

IT

Address latch enable. This input is used to control transparent latches on

the address bus

A[31:0]

,

nBWTT

,

nRW

change during

MCLK

HIGH, but they may be held by driving

See

·

13.2.2 Tald measurement on page 13-3

and

LOCK

. Normally these signals

ALE

LOW.

.

D[31:0]

ITOTZ

Data bus. These are bidirectional signal paths used for data transfers

between the processor and external memory. For read operations (when

nRW

is LOW), the input data must be valid before the falling edge of

MCLK

. For write operations (when

nRW

become valid while

MCLK

is LOW. At high clock frequencies the data may

not become valid until just after the

MCLK

Signals on page 13-3

).

is HIGH), the output data will

rising edge (see

·

13.3 Main Bus

DBE

IT

Data bus enable. When this input is LOW, the data bus,

a high impedance state (Note 1). The drivers will always be high

impedance except during write operations, and

in systems which do not require the data bus for DMA or similar activities.

D[31:0]

is put into

DBE

must be driven HIGH

FCLK

ICK

Fast clock input. When the

performing an internal cycle, it is clocked with the Fast Clock,

ARM610

CPU is accessing the cache or

FCLK

.

LOCK

OCZ

Locked operation.

access sequence, and the memory manager should wait until

LOW before allowing another device to access the memory.

changes while

MCLK

is HIGH and remains HIGH during the locked

memory sequence.

LOCK

is latched by

LOCK

is driven HIGH, to signal a

locked

memory

LOCK

LOCK

goes

ALE

.

MCLK

ICK

Memory clock input. This clock times all

LOW or HIGH period of

alternatively, the

nWAIT

achieve similar effects.

ARM610

memory accesses. The

MCLK

input may be used with a free-running

may be stretched for slow peripherals;

MCLK

to

Table 2-1: Signal descriptions

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ARM7TDMI | 32-Bit Advanced RISC Machines(ARM) Microprocessor Core(32位ARM微處理器內(nèi)核芯片) |

| ART10012T | 28V Input, Triple Output / HYBRID - HIGH RELIABILITY RADIATION HARDENED DC/DC CONVERTER |

| ART10015T | 28V Input, Triple Output / HYBRID - HIGH RELIABILITY RADIATION HARDENED DC/DC CONVERTER |

| ART2812T | 28V Input, Triple Output / HYBRID - HIGH RELIABILITY RADIATION HARDENED DC/DC CONVERTER |

| ART28XXT | 28V Input, Triple Output / HYBRID - HIGH RELIABILITY RADIATION HARDENED DC/DC CONVERTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ARM7-009 | 制造商:Gravitech 功能描述:ARM7 LPC2378 W/2.8" TCH SCRN LCD BLU |

| ARM720T | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:General-purpose 32-bit Microprocessor with 8KB cache, enlarged Write buffer, and Memory Management Unit (MMU) combined in a single chip |

| ARM7DIMM-LPC2478 | 功能描述:模塊化系統(tǒng) - SOM LPC2478 ARM7 DIMM Module, Rev 2.2 RoHS:否 制造商:Digi International 外觀尺寸:ConnectCore 9P 處理器類(lèi)型:ARM926EJ-S 頻率:150 MHz 存儲(chǔ)容量:8 MB, 16 MB 存儲(chǔ)類(lèi)型:NOR Flash, SDRAM 接口類(lèi)型:I2C, SPI, UART 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 尺寸:1.97 in x 1.97 in x 6.1 in |

| ARM7TDI | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:周立功的中文ARM7TDI文檔 |

| ARM7TDMI | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:general purpose 32-bit microprocessors |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。