- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄298893 > BXM80526B600128 (INTEL CORP) 64-BIT, 600 MHz, MICROPROCESSOR, PBGA495 PDF資料下載

參數(shù)資料

| 型號(hào): | BXM80526B600128 |

| 廠商: | INTEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 64-BIT, 600 MHz, MICROPROCESSOR, PBGA495 |

| 封裝: | BGA2-495 |

| 文件頁(yè)數(shù): | 8/74頁(yè) |

| 文件大小: | 870K |

| 代理商: | BXM80526B600128 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)

Mobile Intel Celeron Processor (0.18) in BGA2 and Micro-PGA2 Packages

at 700MHz, 650 MHz, 600 MHz, 550 MHz, 500 MHz, 450 MHz,

Low-voltage 500 MHz, and Low-voltage 400A MHz

Datasheet

Order#-XXX

9

2.3

GTL+ Signals

The mobile Celeron processor system bus signals use a variation of the low-voltage swing GTL

signaling technology. The mobile Celeron processor system bus specification is similar to the

Pentium II processor system bus specification, which is a version of GTL with enhanced noise

margins and less ringing.

The GTL+ system bus depends on incident wave switching and uses flight time for timing

calculations of the GTL+ signals, as opposed to capacitive derating. Analog signal simulation of

the system bus including trace lengths is highly recommended. Contact your field sales

representative to receive the IBIS models for the mobile Celeron processor.

The GTL+ system bus of the Celeron processor was designed to support high-speed data transfers

with multiple loads on a long bus that behaves like a transmission line. However, in mobile

systems the system bus only has two loads (the processor and the chipset) and the bus traces are

short. It is possible to change the layout and termination of the system bus to take advantage of the

mobile environment using the same GTL+ I/O buffers. In mobile systems the GTL+ system bus is

terminated at one end only. This termination is provided on the processor core (except for the

RESET# signal). Refer to the Mobile Pentium III Processor GTL+ System Bus Layout Guideline

for details on laying out the GTL+ system bus.

2.4

Mobile Celeron Processor CPUID

After a power-on RESET or when the CPUID version information is loaded, register EAX and

EBX[7:0] contains the values shown in Table 4. After the L2 cache is initialized, the CPUID

cache/TLB descriptors will be the values shown in Table 5.

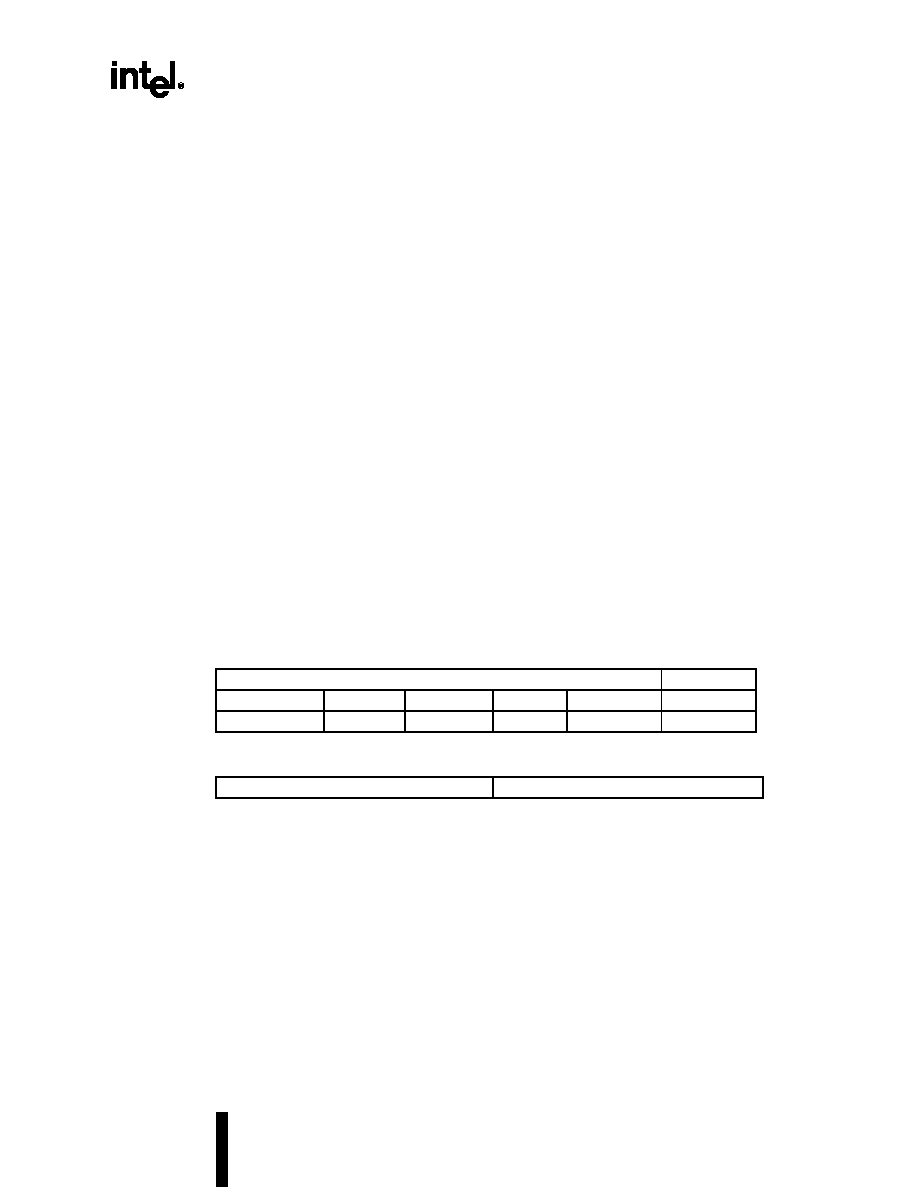

Table 4. Mobile Celeron Processor CPUID

EAX[31:0]

EBX[7:0]

Reserved [31:14]

Type [13:12] Family [11:8]

Model [7:4] Stepping [3:0]

Brand ID

X0

6

8

X

01

Table 5. Mobile Celeron Processor CPUID Cache and TLB Descriptors

Cache and TLB Descriptors

01H, 02H, 03H, 04H, 08H, 0CH, 41H

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BXM80526B700128 | 64-BIT, 700 MHz, MICROPROCESSOR, CPGA495 |

| BXM80526B700 | 64-BIT, 700 MHz, MICROPROCESSOR, CPGA495 |

| BXM80536GC2100F | 32-BIT, 2100 MHz, MICROPROCESSOR, CPGA478 |

| BXM80536GC1800F | 32-BIT, 1800 MHz, MICROPROCESSOR, CPGA478 |

| BXM80536GC1600F | 32-BIT, 1600 MHz, MICROPROCESSOR, CPGA478 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BXM80536NC1400ES L7LS | 制造商:Intel 功能描述:CELERON M,360,1.40GHZ,1M CACHE, 400MHZ FSB,1.26V,UFCPGA - Boxed Product (Development Kits) |

| BXMP1000 | 制造商:SPECTRUM 制造商全稱:Spectrum Microwave, Inc. 功能描述:RF AMPLIFIER |

| BXMP1001 | 制造商:SPECTRUM 制造商全稱:Spectrum Microwave, Inc. 功能描述:RF AMPLIFIER |

| BXMP1002 | 制造商:SPECTRUM 制造商全稱:Spectrum Microwave, Inc. 功能描述:RF AMPLIFIER |

| BXMP1003 | 制造商:SPECTRUM 制造商全稱:Spectrum Microwave, Inc. 功能描述:RF AMPLIFIER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。