- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1909 > CS61584A-IQ3Z (Cirrus Logic Inc)IC LINE INTERFACE T1/E1 64LQFP PDF資料下載

參數(shù)資料

| 型號: | CS61584A-IQ3Z |

| 廠商: | Cirrus Logic Inc |

| 文件頁數(shù): | 44/47頁 |

| 文件大小: | 0K |

| 描述: | IC LINE INTERFACE T1/E1 64LQFP |

| 標準包裝: | 160 |

| 接口: | 并行/串行 |

| 電源電壓: | 3.3V,5V |

| 封裝/外殼: | 64-LQFP |

| 供應商設備封裝: | 64-LQFP(10x10) |

| 包裝: | 托盤 |

| 安裝類型: | 表面貼裝 |

| 產(chǎn)品目錄頁面: | 759 (CN2011-ZH PDF) |

| 其它名稱: | 598-1713 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁當前第44頁第45頁第46頁第47頁

CS61584A

6

DS261PP5

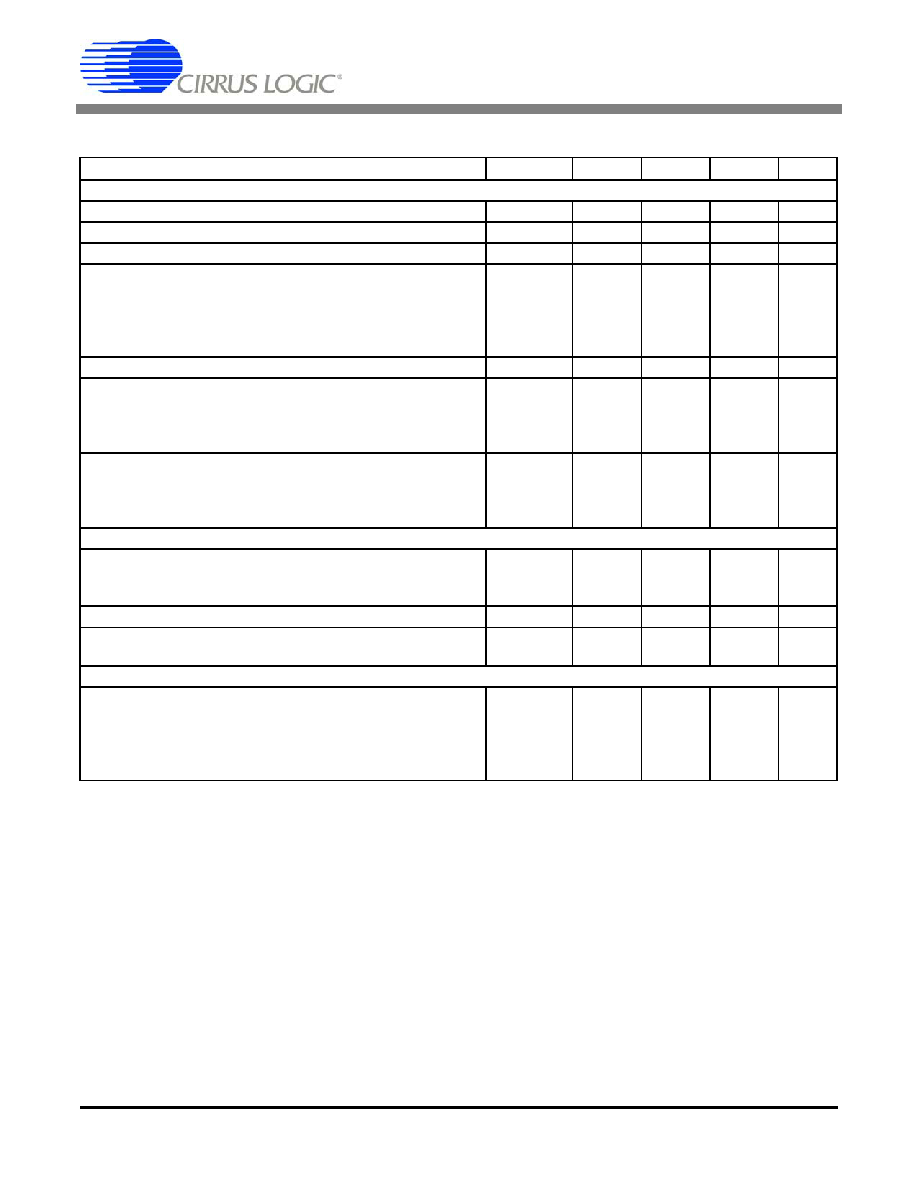

ANALOG CHARACTERISTICS (T

A = -40 to 85 °C; power supply pins within ±5% of nominal.)

Notes: 7. For input amplitude of 1.2 Vpk to 4.14 Vpk.

8. For input amplitude of 0.5 Vpk to 1.2 Vpk, and 4.14 Vpk to 5.0 Vpk.

9. For input amplitude of 1.07 Vpk to 4.14 Vpk.

10. For input amplitude of 4.14 Vpk to 5.0 Vpk.

11. Jitter tolerance increases at lower frequencies. Refer to the Receiver section.

12. Not production tested. Parameters guaranteed by design and characterization.

13. Typical performance using the line interface circuitry recommended in the Applications section.

14. Return loss = 20 log10 ABS((z1 + z0) / (z1 - z0)) where z1 = impedance of the transmitter or receiver, and

z0 = cable impedance.

15. Attenuation measured with sinusoidal input jitter equal to 3/4 of measured jitter tolerance. Circuit

attenuates jitter at 20 dB/decade above the corner frequency. Output jitter can increase significantly

when more than 28 UI's are input to the attenuator. The jitter attenuator -3 dB knee in T1 mode is

selectable for 4.0 Hz or 1.25 Hz. Refer to the Jitter Attenuator section.

Parameter

Symbol

Min

Typ

Max

Unit

Receiver

RTIP/RRING Differential Input Impedance

-

20

-

k

Sensitivity Below DSX-1 (0 dB = 2.4 V)

-

-13.6

-

dB

Loss of Signal Threshold

-

0.3

-

V

Data Decision Threshold

T1, DSX-1

(Note 7)

(Note 8)

T1, FCC Part 68 and E1

(Note

(Note 10)

60

55

45

40

65

-

50

-

70

75

55

60

% of

Peak

Allowable Consecutive Zeros before LOS

160

175

190

bits

Receiver Input Jitter Tolerance (DSX-1, E1)

10 Hz and below

(Note 11)

2kHz

10 kHz - 100 kHz

300

6.0

0.4

-

UI

Receiver Return Loss

51 kHz - 102 kHz

102 kHz - 2.048 MHz

2.048 MHz - 3.072 MHz

12

18

14

22

24

22

-

dB

Jitter Attenuator

Jitter Attenuator Corner Frequency

T1

E1

1.25

-

4.0

1.25

-

Hz

Attenuation at 10 kHz Jitter Frequency

-

60

-

dB

Attenuator Input Jitter Tolerance

(Note 12)

(Before Onset of FIFO Overflow or Underflow Protection)

28

43

-

UIpk-pk

Transmitter

Arbitrary Pulse Amplitude at Transformer Secondary

T1, DSX-1

T1, DS1

E1, 75

E1, 120

-

73

52

43

52

-

mV/LS

B

CS61584A

6

DS261F1

相關PDF資料 |

PDF描述 |

|---|---|

| CS61884-IRZ | IC LN INTERF T1/E1/J1 160-LFBGA |

| CS8130-CS | IC IR TRANSCEIVER 2-5V 20-SSOP |

| CS8190EDWF20G | IC TACH/SPEEDO DRVR PREC 20SOICW |

| CS8191XNF16 | IC DRVR AIRCORE TACH/SPEED 16DIP |

| CS82C5296 | IC UART/BRG 5V 16MHZ 28-PLCC |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| CS61584A-IQ3ZR | 功能描述:網(wǎng)絡控制器與處理器 IC IC 3.3V/5V Dul T1/E1 Line Intrfc Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| CS61584A-IQ5 | 功能描述:網(wǎng)絡控制器與處理器 IC IC 3.3V/5V Dual T1/ E1 Line Intrfc Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| CS61584A-IQ5Z | 功能描述:網(wǎng)絡控制器與處理器 IC IC 3.3V/5V Dual T1/ E1 Line Intrfc Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| CS61584A-IQ5ZR | 功能描述:網(wǎng)絡控制器與處理器 IC IC 3.3V/5V Dul T1/E1 Line Intrfc Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| CS61584-IL3 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Line Interface |

發(fā)布緊急采購,3分鐘左右您將得到回復。