- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1913 > DS1876T+T&R (Maxim Integrated Products)IC CTRLR SFP DUAL LDD 28TQFN PDF資料下載

參數(shù)資料

| 型號(hào): | DS1876T+T&R |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 14/69頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC CTRLR SFP DUAL LDD 28TQFN |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 2,500 |

| 類型: | SFP 激光控制器 |

| 輸入類型: | 邏輯 |

| 輸出類型: | 邏輯 |

| 接口: | I²C |

| 電流 - 電源: | 10mA |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 28-WFQFN 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 28-TQFN-EP(5x5) |

| 包裝: | 帶卷 (TR) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁

21

Maxim Integrated

SFP Controller with Dual LDD Interface

DS1876

always the second byte transmitted during a write

operation following the slave address byte.

I2C Protocol

See Figure 13 for an example of I2C timing.

Writing a Single Byte to a Slave: The master must

generate a START condition, write the slave address

byte (R/W = 0), write the memory address, write

the byte of data, and generate a STOP condition.

Remember that the master must read the slave’s

acknowledgement during all byte write operations.

Writing Multiple Bytes to a Slave: To write multiple

bytes to a slave, the master generates a START condi-

tion, writes the slave address byte (R/W = 0), writes

the memory address, writes up to 8 data bytes, and

generates a STOP condition. The DS1876 writes 1 to

8 bytes (one page or row) with a single write trans-

action. This is internally controlled by an address

counter that allows data to be written to consecutive

addresses without transmitting a memory address

before each data byte is sent. The address counter

limits the write to one 8-byte page (one row of the

memory map). Attempts to write to additional pages

of memory without sending a STOP condition between

pages result in the address counter wrapping around

to the beginning of the present row.

For example: A 3-byte write starts at address 06h and

writes three data bytes (11h, 22h, and 33h) to three

“consecutive” addresses. The result is that addresses

06h and 07h would contain 11h and 22h, respec-

tively, and the third data byte, 33h, would be written

to address 00h.

To prevent address wrapping from occurring, the

master must send a STOP condition at the end of

the page, then wait for the bus-free or EEPROM write

time to elapse. Then the master can generate a new

START condition and write the slave address byte

(R/W = 0) and the first memory address of the next

memory row before continuing to write data.

Acknowledge Polling: Any time a EEPROM page is

written, the DS1876 requires the EEPROM write time

(tWR) after the STOP condition to write the contents of

the page to EEPROM. During the EEPROM write time,

the DS1876 does not acknowledge its slave address

because it is busy. It is possible to take advantage

of that phenomenon by repeatedly addressing the

DS1876, which allows the next page to be written

as soon as the DS1876 is ready to receive the data.

The alternative to acknowledge polling is to wait for

maximum period of tWR to elapse before attempting

to write again to the DS1876.

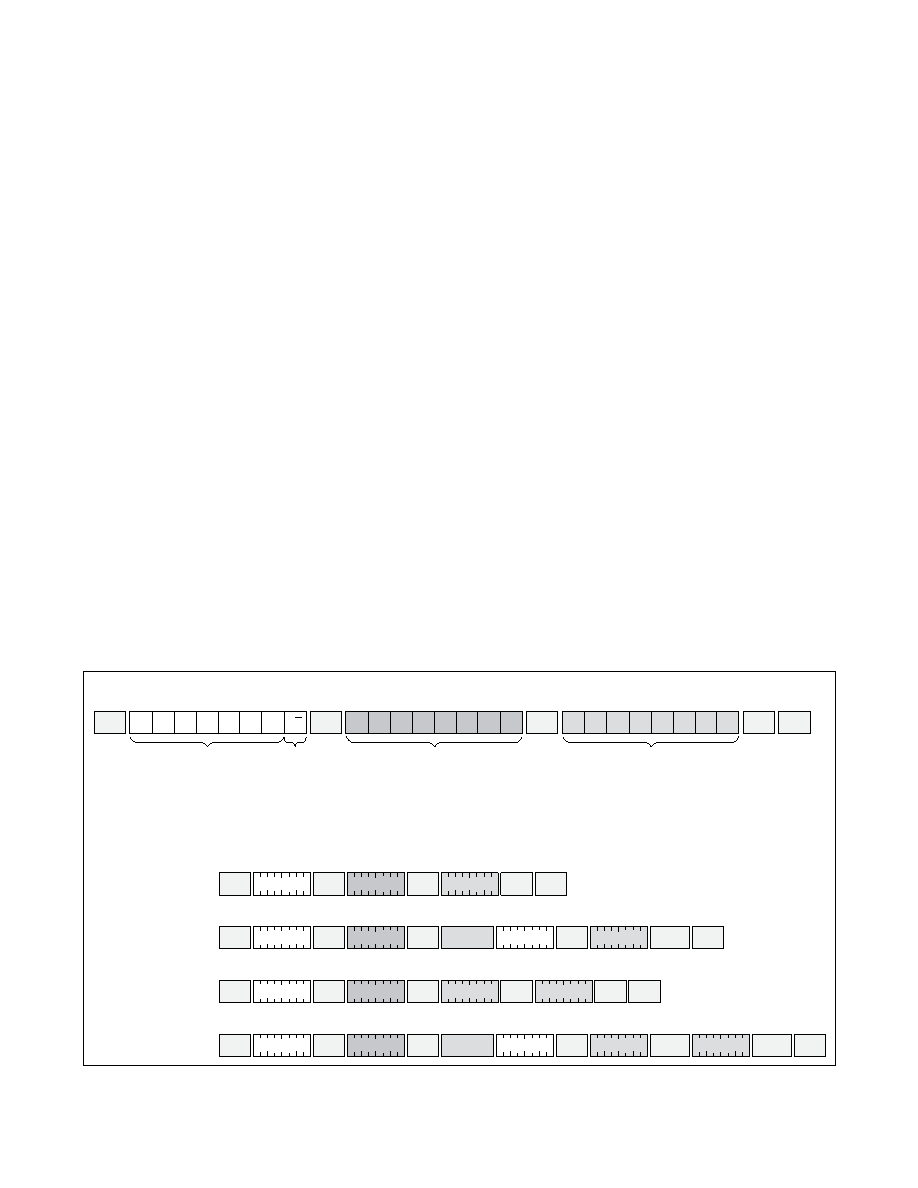

Figure 13. Example I2C Timing

START

STOP

SLAVE

ACK

SLAVE

ACK

STOP

SINGLE-BYTE WRITE

-WRITE 00h TO REGISTER BAh

TWO-BYTE WRITE

-WRITE 01h AND 75h TO

REGISTERS C8h AND C9h

SINGLE-BYTE READ

-READ REGISTER BAh

TWO-BYTE READ

-READ C8h AND C9h

REPEATED

START

MASTER

NACK

1 0 1 0 0 0 1 0

A2h

1 0 1 1 1 0 1 0

BAh

SLAVE

ACK

START

SLAVE

ACK

1 0 1 0 0 0 1 0

A2h

1 0 1 0 0 0 1 1

A3h

1 0 1 1 1 0 1 0

BAh

SLAVE

ACK

SLAVE

ACK

STOP

0 0 0 0 0 0 0 0

00h

STOP

SLAVE

ACK

STOP

0 1 1 1 0 1 0 1

75h

START

SLAVE

ACK

1 0 1 0 0 0 1 0

A2h

1 1 0 0 1 0 0 0

C8h

SLAVE

ACK

SLAVE

ACK

0 0 0 0 0 0 0 1

01h

SLAVE

ACK

DATA IN BAh

DATA

REPEATED

START

MASTER

ACK

START

SLAVE

ACK

1 0 1 0 0 0 1 0

A2h

1 0 1 0 0 0 1 1

A3h

1 1 0 0 1 0 0 0

C8h

SLAVE

ACK

SLAVE

ACK

DATA IN C8h

DATA

MASTER

NACK

DATA IN C9h

DATA

EXAMPLE I2C TRANSACTIONS WITH A2h AS THE SLAVE ADDRESS

*IF ASEL IS 0, THE SLAVE ADDRESS IS A0h FOR THE AUXILIARY MEMORY AND A2h/B2h FOR THE MAIN MEMORY.

IF ASEL = 1, THE SLAVE ADDRESS IS DETERMINED BY TABLE 02h, REGISTER 8Bh FOR THE MAIN MEMORY. THE AUXILIARY MEMORY CONTINUES TO BE ADDRESSED AT A0h, EXCEPT WHEN THE PROGRAMMED

ADDRESS FOR THE MAIN MEMORY IS A0h.

TYPICAL I2C WRITE TRANSACTION

A)

C)

B)

D)

MSB

LSB

b7

b6

b5

b4

b3

b2

b1

b0

REGISTER ADDRESS

MSB

LSB

b7

b6

b5

b4

b3

b2

b1

b0

DATA

SLAVE

ACK

SLAVE

ACK

SLAVE

ADDRESS*

X

0

1

R/W

MSB

LSB

READ/

WRITE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS1877T+T&R | IC CTLR/MON SFP 1-2CH 28TQFN |

| DS1878T+T&R | IC CTLR SFP W/DGTL LDD RX 28TQFN |

| DS1881Z-050+T&R | IC DGTL POT NV 2CH 45K 16-SOIC |

| DS1882Z-050+T&R | IC POT DIGIT DL LOG 50K 16SOIC |

| DS1884AT+T | IC SFP PON ONU CTRLR 24TQFN |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS1877 | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:SFP Controller for Dual Rx Interface |

| DS1877T+ | 功能描述:ADC / DAC多通道 SFP+ Controller w/ Dual RX Interface RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換速率: 分辨率:8 bit 接口類型:SPI 電壓參考: 電源電壓-最大:3.6 V 電源電壓-最小:2 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-40 |

| DS1877T+T&R | 制造商:Maxim Integrated Products 功能描述:SFP CTRLR FOR DUAL RX INTERFACE TQF - Tape and Reel 制造商:Maxim Integrated Products 功能描述:IC CTLR/MON SFP 1-2CH 28TQFN |

| DS1877T+T&R | 功能描述:ADC / DAC多通道 SFP+ Controller w/ Dual RX Interface RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換速率: 分辨率:8 bit 接口類型:SPI 電壓參考: 電源電壓-最大:3.6 V 電源電壓-最小:2 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-40 |

| DS1877T+TR | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:SFP Controller for Dual Rx Interface |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。