- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄1915 > DS3141+ (Maxim Integrated Products)IC FRAMER DS3/E3 SNGL 144CSBGA PDF資料下載

參數(shù)資料

| 型號(hào): | DS3141+ |

| 廠商: | Maxim Integrated Products |

| 文件頁(yè)數(shù): | 18/88頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC FRAMER DS3/E3 SNGL 144CSBGA |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 160 |

| 控制器類型: | DS3/E3 調(diào)幀器 |

| 接口: | LIU |

| 電源電壓: | 3.135 V ~ 3.465 V |

| 電流 - 電源: | 80mA |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 144-BGA,CSPBGA |

| 供應(yīng)商設(shè)備封裝: | 144-TECSBGA(13x13) |

| 包裝: | 托盤(pán) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)當(dāng)前第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)

DS3141/DS3142/DS3143/DS3144 Single/Dual/Triple/Quad DS3/E3 Framers

25 of 88

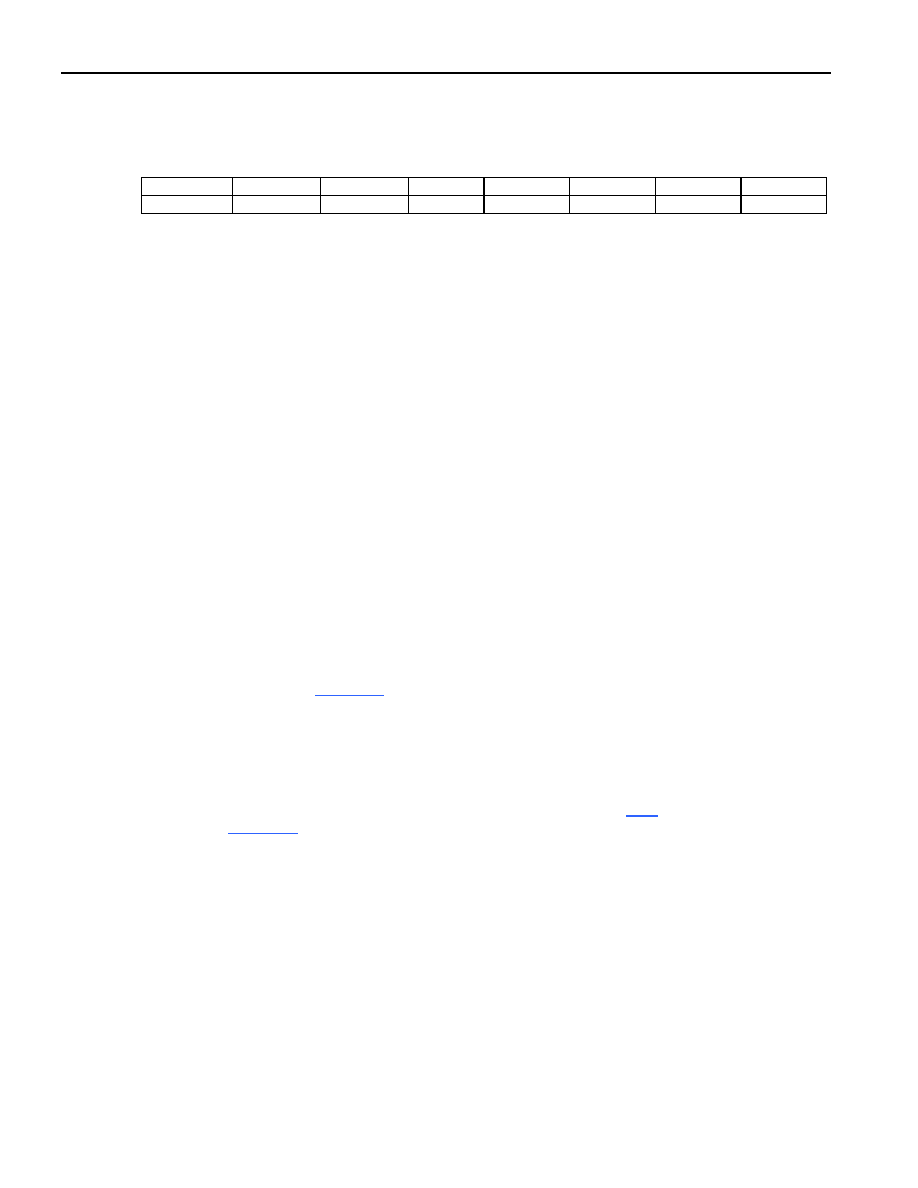

Register Name:

MC3

Register Description:

Master Configuration Register 3

Register Address:

03h

Bit #

7

6

5

4

3

2

1

0

Name

TDENMS

TSOFC

TOHENI

TOHI

TSOFI

TICLKI

TDATI

TDENI

Default

0

Bit 0: TDEN Invert Enable (TDENI)

0 = do not invert the TDEN/TGCLK signal (normal mode)

1 = invert the TDEN/TGCLK signal (inverted mode)

Bit 1: TDAT Invert Enable (TDATI)

0 = do not invert the TDAT signal (normal mode)

1 = invert the TDAT signal (inverted mode)

Bit 2: TICLK Invert Enable (TICLKI)

0 = do not invert the TICLK signal (normal mode)

1 = invert the TICLK signal (inverted mode)

Bit 3: TSOF Invert Enable (TSOFI)

0 = do not invert the TSOF signal (normal mode)

1 = invert the TSOF signal (inverted mode)

Bit 4: TOH Invert Enable (TOHI)

0 = do not invert the TOH signal (normal mode)

1 = invert the TOH signal (inverted mode)

Bit 5: TOHEN Invert Enable (TOHENI)

0 = do not invert the TOHEN signal (normal mode)

1 = invert the TOHEN signal (inverted mode)

Bit 6: Transmit Start-of-Frame I/O Control (TSOFC). When this bit is logic 1, the TSOF pin is an output and

pulses for the last TICLK cycle of each frame. When this bit is 0, the TSOF pin is an input, and the device uses it to

determine the frame boundaries. See Figure 5-1 for functional timing information.

0 = TSOF is an input (reset default as input)

1 = TSOF is an output

Bit 7: Transmit Data-Enable Mode Select (TDENMS). When this bit is logic 0, the TDEN/TGCLK output has the

TDEN (data enable) function. TDEN asserts during payload bit times and de-asserts during overhead bit times.

When this bit is logic 1, TDEN/TGCLK has the TGCLK (gapped clock) function. TGCLK pulses during payload bit

times and is suppressed during overhead bit times. The TCCLK control bit in the MC2 register has precedence

over this control bit. See Figure 5-1 for functional timing information.

0 = TDEN (data enable) mode

1 = TGCLK (gapped clock) mode

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS31412N | IC 12CH DS3/3 FRAMER 349-BGA |

| DS3150TN | IC LIU T3/E3/STS-1 IND 48-TQFP |

| DS3154N+ | IC LIU DS3/E3/STS-1 QD 144CSBGA |

| DS3164+ | IC ATM/PACKET PHY QUAD 400-BGA |

| DS3170+ | IC TXRX DS3/E3 100-CSBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS3141+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Single DS3/E3 Framer RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS314-1010NR WAF | 制造商:ON Semiconductor 功能描述: |

| DS31412 | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 12 Port DS3/E3 Framer RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS31412N | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 12 Port DS3/E3 Framer RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS31415 | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:3-Input, 4-Output, Single DPLL Timing IC with Sub-ps Output Jitter and 1588 Clock |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。