- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377001 > DSP56F801 (飛思卡爾半導(dǎo)體(中國(guó))有限公司) 16-bit Hybrid Controller(16位混合控制器) PDF資料下載

參數(shù)資料

| 型號(hào): | DSP56F801 |

| 廠商: | 飛思卡爾半導(dǎo)體(中國(guó))有限公司 |

| 英文描述: | 16-bit Hybrid Controller(16位混合控制器) |

| 中文描述: | 16位混合控制器(16位混合控制器) |

| 文件頁(yè)數(shù): | 8/44頁(yè) |

| 文件大小: | 858K |

| 代理商: | DSP56F801 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)

8

56F801 Technical Data

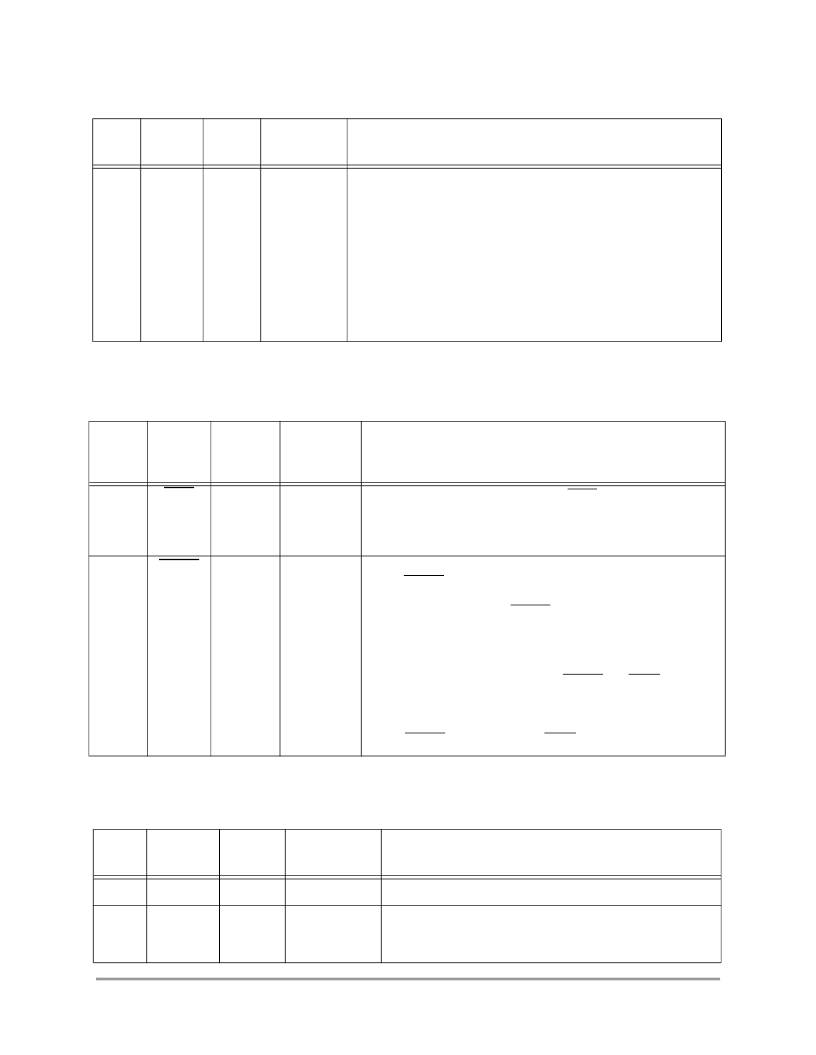

2.4 Interrupt and Program Control Signals

2.5 Pulse Width Modulator (PWM) Signals

Table 8. Pulse Width Modulator (PWMA) Signals

1

XTAL

GPIOB3

Output

Input/

Output

Chip-

driven

Input

Crystal Oscillator Output

—This output should be connected to an

8MHz external crystal or ceramic resonator. For more information,

please refer to

Section 3.5

.

This pin can also be connected to an external clock source. For more

information, please refer to

Section 3.5.3

.

Port B GPIO

—This multiplexed pin is a General Purpose I/O (GPIO)

pin that can be programmed as an input or output pin. This I/O can be

utilized when using the on-chip relaxation oscillator so the XTAL pin is

not needed.

Table 7. Interrupt and Program Control Signals

No. of

Pins

Signal

Name

Signal

Type

State

During

Reset

Signal Description

1

IRQA

Input

(Schmitt)

Input

External Interrupt Request A

—The IRQA input is a

synchronized external interrupt request that indicates that an

external device is requesting service. It can be programmed to be

level-sensitive or negative-edge- triggered.

1

RESET

Input

(Schmitt)

Input

Reset

—This input is a direct hardware reset on the processor.

When RESET is asserted low, the hybrid controller is initialized

and placed in the Reset state. A Schmitt trigger input is used for

noise immunity. When the RESET pin is deasserted, the initial

chip operating mode is latched from the EXTBOOT pin. The

internal reset signal will be deasserted synchronous with the

internal clocks, after a fixed number of internal clocks.

To ensure complete hardware reset, RESET and TRST should be

asserted together. The only exception occurs in a debugging

environment when a hardware device reset is required and it is

necessary not to reset the OnCE/JTAG module. In this case,

assert RESET, but do not assert TRST.

No. of

Pins

Signal

Name

Signal

Type

State During

Reset

Signal Description

6

PWMA0-5

Output

Tri-stated

PWMA0-5

— These are six PWMA output pins.

1

FAULTA0

Input

(Schmitt)

Input

FAULTA0

— This fault input pin is used for disabling selected

PWMA outputs in cases where fault conditions originate off-

chip.

Table 6. PLL and Clock (Continued)

No. of

Pins

Signal

Name

Signal

Type

State

During Reset

Signal Description

F

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DSP56F803E | 16-bit Digital Signal Controllers |

| DSP56F805E | 16-bit Digital Signal Controllers |

| DSP56F805FV80E | 16-bit Digital Signal Controllers |

| DSP56F805 | 16-bit Hybrid Controller(16位混合控制器) |

| DSP56F807PY80E | 16-bit Digital Signal Controllers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DSP56F801-7UM | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:16-bit Digital Signal Controllers |

| DSP56F801E | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:56F801 16-bit Hybrid Controller |

| DSP56F801EVM | 功能描述:開(kāi)發(fā)板和工具包 - 其他處理器 Evaluation Kit For DSP56F801 RoHS:否 制造商:Freescale Semiconductor 產(chǎn)品:Development Systems 工具用于評(píng)估:P3041 核心:e500mc 接口類型:I2C, SPI, USB 工作電源電壓: |

| DSP56F801EVMUM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:56F801 Evaluation Module Hardware User's Manual |

| DSP56F801FA60 | 功能描述:數(shù)字信號(hào)處理器和控制器 - DSP, DSC 60Mhz/30MIPS RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。