- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362688 > EM78P568 (ELAN Microelctronics Corp .) 8-BIT OTP MICRO-CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | EM78P568 |

| 廠商: | ELAN Microelctronics Corp . |

| 英文描述: | 8-BIT OTP MICRO-CONTROLLER |

| 中文描述: | 8位檢察官微控制器 |

| 文件頁數(shù): | 22/61頁 |

| 文件大小: | 568K |

| 代理商: | EM78P568 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁

EM78P568

8-bit OTP Micro-controller

__________________________________________________________________________________________________________________________________________________________________

* This specification are subject to be changed without notice.

01/31/2004 V4.7

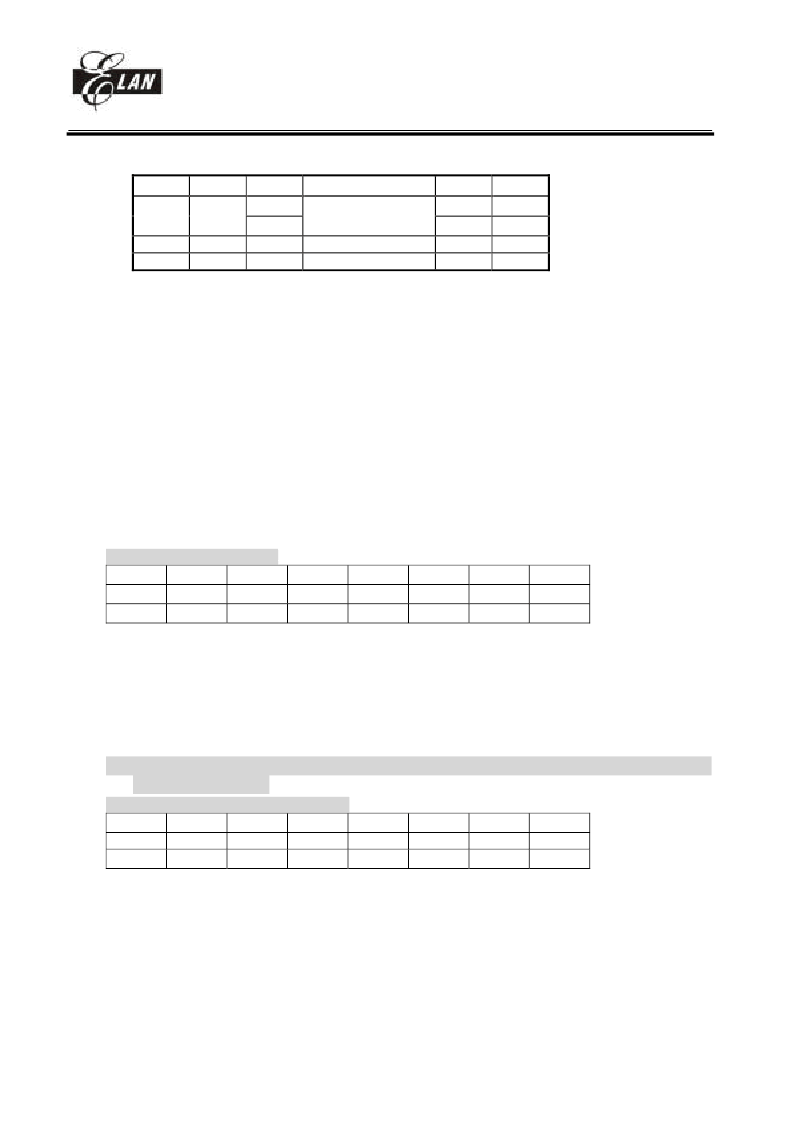

Bit 1 ~ Bit 2 (LCD_C0 ~ LCD_C1) : LCD display control

LCD_C1 LCD_C0 LCD_M LCD Display Control

0

0

0

1

0

1

:

1

1

:

Ps. To change the display duty must set the "LCD_C1 ,LCD_C0" to "00".

The controller can drive LCD directly. The LCD block is made up of common driver, segment driver,

display LCD RAM, common output pins, segment output pins and LCD operating power supply. The basic

structure contains a timing control. This timing control uses the basic frequency 32.768KHz to generate the

proper timing for different duty and display access.

RD PAGE0 Bit 0 ~ Bit 2 are LCD control bits for LCD driver. These LCD control bits determine the duty,

the number of common and the frame frequency. The LCD display (disable, enable, blanking) is controlled

by Bit 1 and Bit 2. The driving duty is decided by Bit 0. The display data is stored in LCD RAM which

address and data access controlled by registers R5 PAGE1 and R6 PAGE1.

User can regulate the contrast of LCD display by IOC5 PAGE0 Bit 0 ~ Bit 3 (BIAS0 ~ BIAS3). Up to 16

levels contrast is convenient for better display.

Bit 3 ~ Bit 6 :

(undefined) not allowed to use

Bit 7 (DETOED) : the interrupt triggering edge control for CTCSS tone detection output

0/1

falling edge/falling and rising

PAGE1 (Counter2 data register)

Bit7

Bit6

Bit5

Bit4

Bit3

CN27

CN26

CN25

CN24

CN23

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

Bit 0 ~ Bit 7 (CN20 ~ CN27) : Counter2's buffer that user can read and write.

Counter2 is a 8-bit up-counter with 8-bit prescaler that user can use RD PAGE1 to preset and read the

counter.(write

preset) After a interruption, it will reload the preset value.

Example for writing :

MOV 0x0D, A ; write the data at accumulator to counter2 (preset)

Example for reading :

MOV A, 0x0D ; read the data at counter2 to accumulator

RE (Interrupt flag, Wake-up control, DAC tone output frequency selection, PWM2 duty latch,

Multiplication result)

PAGE0 (Interrupt flag, Wake-up control bits)

7

6

5

4

3

-

-

-

-

/WUP83

R/W-0

Bit 0 (/WUP80) : PORT80 wake-up control, 0/1

disable/enable P80 pin wake-up function

Bit 1 (/WUP81) : PORT81 wake-up control, 0/1

disable/enable P81 pin wake-up function

Bit 2 (/WUP82) : PORT82 wake-up control, 0/1

disable/enable P82 pin wake-up function

Bit 3 (/WUP83) : PORT83 wake-up control, 0/1

disable/enable P83 pin wake-up function

Bit 4 ~ Bit 7 :

(undefined) not allowed to use

Set when a selected period is reached, reset by software.

Duty

1/4

1/2

:

:

Bias

1/3

1/3

:

:

change duty

Disable(turn off LCD)

Blanking

LCD display enable

Bit2

CN22

R/W-0

Bit1

CN21

R/W-0

Bit0

CN20

R/W-0

2

1

0

/WUP82

R/W-0

/WUP81

R/W-0

/WUP80

R/W-0

相關PDF資料 |

PDF描述 |

|---|---|

| EM78P569 | 8 - BIT OTP MICRO CONTROLLER |

| EM78P5840 | 8 BIT MICROCONTROLLER |

| EM78P5841 | 8 BIT MICROCONTROLLER |

| EM78P5842 | 8 BIT MICROCONTROLLER |

| EM78P809N | 8-BIT MICROCONTROLLER |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| EM7A8620 | 制造商:EMC 制造商全稱:ELAN Microelectronics Corp 功能描述:Voice over IP |

| EM7G | 制造商:GULFSEMI 制造商全稱:Gulf Semiconductor 功能描述:ULTRAFAST EFFICIENT PLASTIC SILICON RECTIFIER VOLTAGE: 1000V CURRENT: 1.0A |

| EM800 | 制造商:EDI 制造商全稱:Electronic devices inc. 功能描述:HIGH VOLTAGE HIGH CURRENT MINIATURE RECTIFIERS |

| EM8000EHP | 制造商:JDSU 制造商全稱:JDS Uniphase Corporation 功能描述:The industrya??s most compact 100 G test solution |

| EM800-DCM | 制造商:MRV 制造商全稱:MRV 功能描述:LambdaDriver Dispersion Compensation Module (EM800/1600-DCM and DCMD) |

發(fā)布緊急采購,3分鐘左右您將得到回復。