- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362688 > EM78P568 (ELAN Microelctronics Corp .) 8-BIT OTP MICRO-CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | EM78P568 |

| 廠商: | ELAN Microelctronics Corp . |

| 英文描述: | 8-BIT OTP MICRO-CONTROLLER |

| 中文描述: | 8位檢察官微控制器 |

| 文件頁數(shù): | 26/61頁 |

| 文件大?。?/td> | 568K |

| 代理商: | EM78P568 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁

EM78P568

8-bit OTP Micro-controller

__________________________________________________________________________________________________________________________________________________________________

* This specification are subject to be changed without notice.

01/31/2004 V4.7

VII.3 Special Purpose Registers

A (Accumulator)

Internal data transfer, or instruction operand holding

It's not an addressable register.

CONT (Control Register)

7

6

P70EG

INT

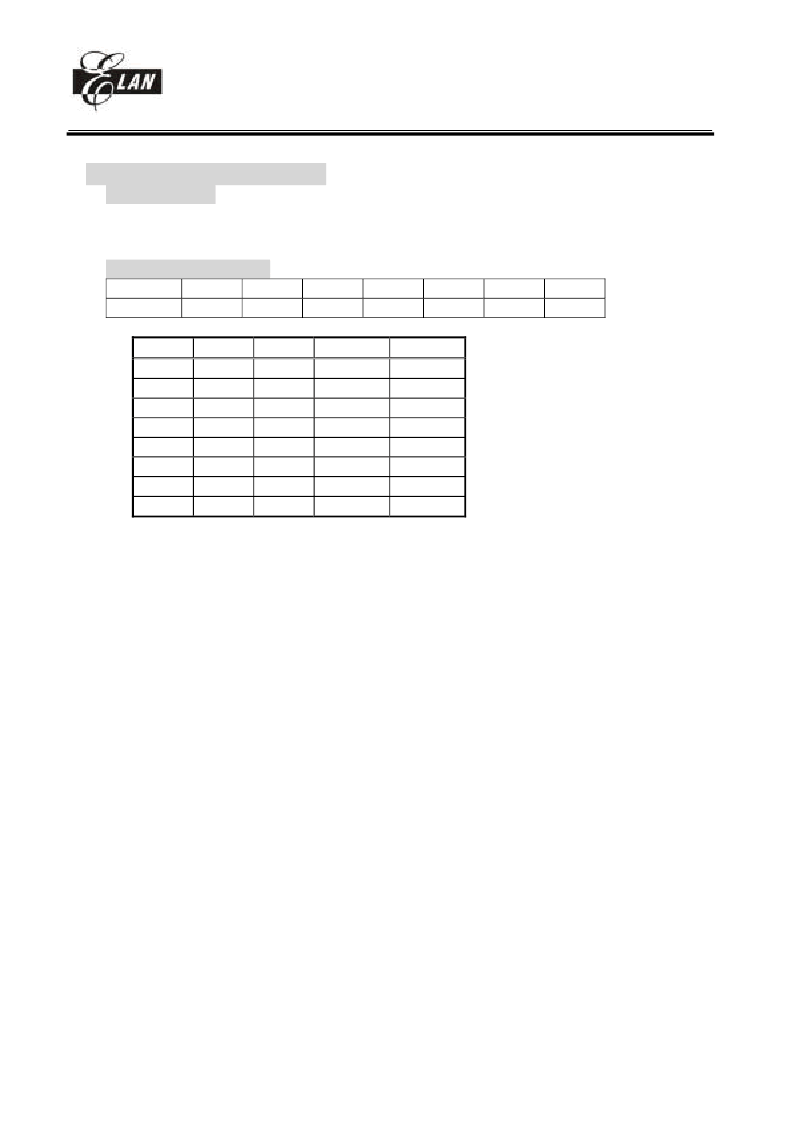

Bit 0 ~ Bit 2 (PSR0 ~ PSR2) : TCC/WDT prescaler bits

PSR2

PSR1

0

0

0

0

0

1

0

1

1

0

1

0

1

1

1

1

Bit 3(PAB) : Prescaler assignment bit

0/1

TCC/WDT

Bit 4(RETBK) : Return value backup control for interrupt routine

0

disable/enable

When this bit is set to 1, the CPU will store ACC,R3 status and R5 PAGE automatically after an interrupt is

triggered. And it will be restored after instruction RETI. When this bit is set to 0, the user need to store ACC,

R3 and R5 PAGE in user program.

Bit 5(TS) : TCC signal source

0

internal instruction cycle clock

1

16.384kHz

Bit 6 (INT) : INT enable flag

0

interrupt masked by DISI or hardware interrupt

1

interrupt enabled by ENI/RETI instructions

Bit 7(P70EG) : interrupt edge type of P70

0

P70 's interruption source is a rising edge signal.

1

P70 's interruption source is a falling edge signal.

CONT register is readable (CONTR) and writable (CONTW).

TCC and WDT :

There is an 8-bit counter available as prescaler for the TCC or WDT. The prescaler is available for the TCC

only or WDT only at the same time.

An 8 bit counter is available for TCC or WDT determined by the status of the bit 3 (PAB) of the CONT

register.

See the prescaler ratio in CONT register.

Fig.17 depicts the circuit diagram of TCC/WDT.

Both TCC and prescaler will be cleared by instructions which write to TCC each time.

The prescaler will be cleared by the WDTC and SLEP instructions, when assigned to WDT mode.

The prescaler will not be cleared by SLEP instructions, when assigned to TCC mode.

5

TS

4

3

2

1

0

RETBK

PAB

PSR2

PSR1

PSR0

PSR0

0

1

0

1

0

1

0

1

TCC rate

1:2

1:4

1:8

1:16

1:32

1:64

1:128

1:256

WDT rate

1:1

1:2

1:4

1:8

1:16

1:32

1:64

1:128

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EM78P569 | 8 - BIT OTP MICRO CONTROLLER |

| EM78P5840 | 8 BIT MICROCONTROLLER |

| EM78P5841 | 8 BIT MICROCONTROLLER |

| EM78P5842 | 8 BIT MICROCONTROLLER |

| EM78P809N | 8-BIT MICROCONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EM7A8620 | 制造商:EMC 制造商全稱:ELAN Microelectronics Corp 功能描述:Voice over IP |

| EM7G | 制造商:GULFSEMI 制造商全稱:Gulf Semiconductor 功能描述:ULTRAFAST EFFICIENT PLASTIC SILICON RECTIFIER VOLTAGE: 1000V CURRENT: 1.0A |

| EM800 | 制造商:EDI 制造商全稱:Electronic devices inc. 功能描述:HIGH VOLTAGE HIGH CURRENT MINIATURE RECTIFIERS |

| EM8000EHP | 制造商:JDSU 制造商全稱:JDS Uniphase Corporation 功能描述:The industrya??s most compact 100 G test solution |

| EM800-DCM | 制造商:MRV 制造商全稱:MRV 功能描述:LambdaDriver Dispersion Compensation Module (EM800/1600-DCM and DCMD) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。