- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375914 > FS6131-01 (Electronic Theatre Controls, Inc.) Programmable Line Lock Clock Generator IC PDF資料下載

參數(shù)資料

| 型號(hào): | FS6131-01 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Programmable Line Lock Clock Generator IC |

| 中文描述: | 可編程線鎖定時(shí)鐘發(fā)生器IC |

| 文件頁(yè)數(shù): | 32/39頁(yè) |

| 文件大小: | 435K |

| 代理商: | FS6131-01 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)當(dāng)前第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)

32

FS6131-01

Programmable Line Lock Clock Generator IC

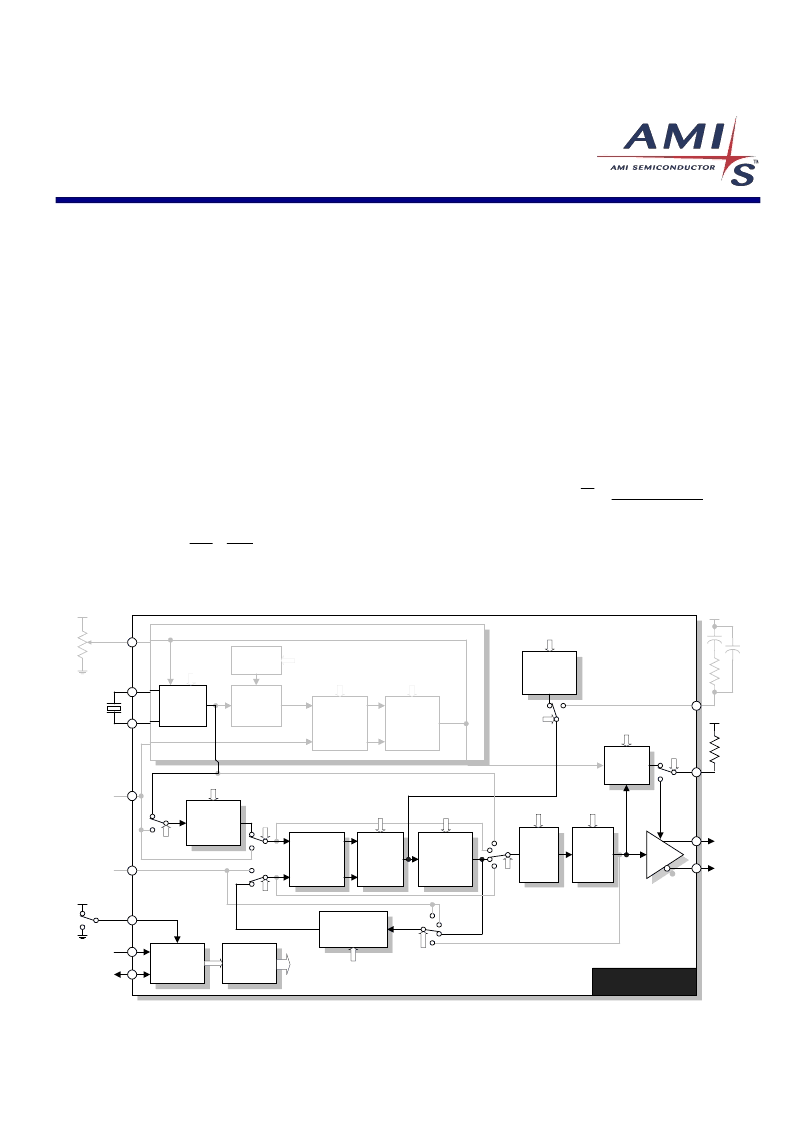

12.0 Device Application:

Stand-Alone Clock Generation

The length of the reference and feedback dividers, their

granularity, and the flexibility of the post Divider make the

FS6131 the most flexible monolithic stand-alone PLL

clock generation device available. The effective block

diagram of the FS6131 when programmed for Stand-

Alone mode is shown in Figure 30.

The source of the Feedback Divider in the Stand-Alone

mode is the output of the VCO. By dividing the input ref-

erence frequency down by Reference Divider (N

R

), then

multiplying it up in the Main Loop through the Feedback

Divider (N

F

), and finally dividing the Main Loop output

frequency by the Post Divider (N

Px

), we have the defining

relationship for this mode. The equation for the output

clock frequency (f

CLK

) can be written as

N

f

f

=

Px

R

F

REF

CLK

N

N

1

,

(Eqn.1)

where the reference source frequency (f

REF

) can be either

supplied by the VCXO or applied to the REF pin.

Great flexibility is permitted in the programming of the

FS6131 to achieve exact desired output frequencies

since three integers are involved in the computation.

12.1

A Visual BASIC program is available to completely pro-

gram the FS6131 based on the given parameters.

Suppose that the reference source frequency is

14.318MHz and the desired output frequency is 100MHz.

First, factor the 14.318MHz reference frequency (which is

four times the NTSC television color sub-carrier) into

prime numbers. The exact expression is

Example Calculation

11

7

5

3

2

81

.

14318181

1

7

2

5

×

×

×

=

=

REF

f

.

Figure 30: Block Diagram: Stand-Alone Clock Generation

FS6131

VCXO

Divider

(optional)

(optional)

CRYSTAL LOOP

MAIN LOOP

VCXO

XOUT

XIN

Control

ROM

XTUNE

(optional)

Reference

Divider

(N

R

)

Phase-

Frequency

Detector

Charge

Pump

DOWN

UP

REF

FBK

Phase-

Frequency

Detector

Charge

Pump

DOWN

UP

Internal

Loop

Filter

EXTLF

I

2

C

Interface

SCL

SDA

ADDR

Registers

POST3[1:0]

POST2[1:0]

POST1[1:0]

REFDIV[11:0]

EXTLF

PDREF

PDFBK

VCOSPD,

OSCTYPE

LFTC

MLCP[1:0]

XLCP[1:0]

XLROM[2:0]

XLPDEN,

XLSWAP

REFDSRC

XCT[3:0],

XLVTEN

(f

REF

)

(f

VCO

)

LOCK/

IPRG

(optional)

Post

Divider

(N

Px

)

Voltage

Controlled

Oscillator

Lock

Detect

CMOS

STAT[1:0]

OM[1:0]

Clock

Gobbler

GBL

Feedback

Divider

(N

F

)

FBKDIV[14:0]

FBKDSRC[1:0]

CMOS/PECL

Output

CLKN

(f

CLK

)

CLKP

R

LF

C

LF

R

IPRG

C

LP

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FS6282 | DUAL PLL CLOCK GENERATOR IC |

| FS6282-03 | DUAL PLL CLOCK GENERATOR IC |

| FS6M07652RTC | Time-Delay Relay; Contacts:SPST-NO; Time Range:0.2 sec. to 20 sec.; Timing Function:Delay-On-Make; Voltage Rating:120V |

| FS6M07652RTCTU | Fairchild Power Switch(FPS) |

| FS6M07652RTCYDT | Fairchild Power Switch(FPS) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FS6131-01G | 制造商:ONSEMI 制造商全稱:ON Semiconductor 功能描述:Programmable Line Lock Clock Generator IC |

| FS6131-01G-XTD | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 I2C PROG PLL CLK RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| FS6131-01G-XTP | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 I2C PROG PLL CLK RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| FS6131-01I-XTD | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 I2C PROG PLL CLK (IND) RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| FS6131-01I-XTP | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 I2C PROG PLL CLK IND RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。