- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299161 > GS8150V36AB-300IT (GSI TECHNOLOGY) 512K X 36 LATE-WRITE SRAM, 1.6 ns, PBGA119 PDF資料下載

參數(shù)資料

| 型號: | GS8150V36AB-300IT |

| 廠商: | GSI TECHNOLOGY |

| 元件分類: | SRAM |

| 英文描述: | 512K X 36 LATE-WRITE SRAM, 1.6 ns, PBGA119 |

| 封裝: | FBGA-119 |

| 文件頁數(shù): | 8/25頁 |

| 文件大小: | 885K |

| 代理商: | GS8150V36AB-300IT |

GS8150V18/36AB-357/333/300/250

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

Rev: 1.08 9/2008

16/25

2003, GSI Technology

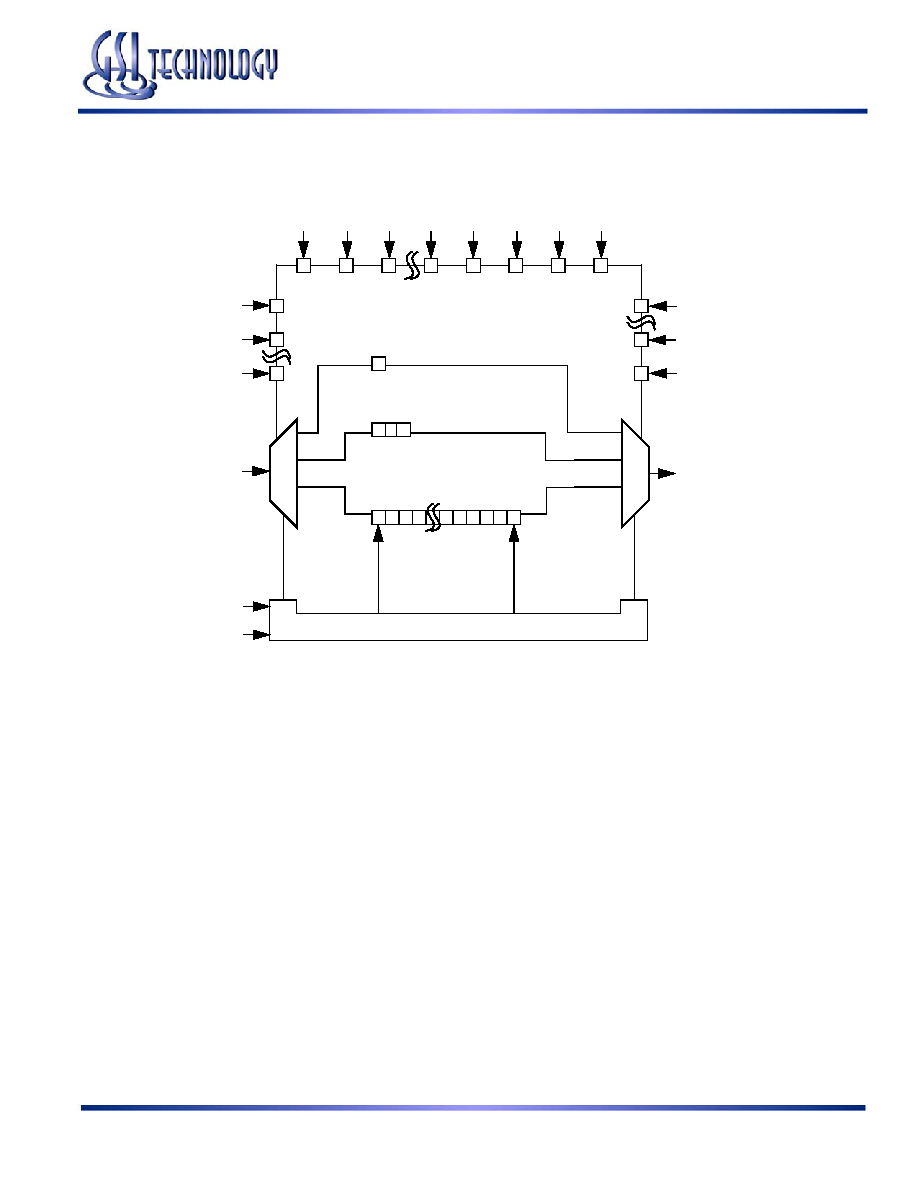

JTAG TAP Block Diagram

Identification (ID) Register

The ID Register is a 32-bit register that is loaded with a device and vendor specific 32-bit code when the controller is put in

Capture-DR state with the IDCODE command loaded in the Instruction Register. The code is loaded from a 32-bit on-chip ROM.

It describes various attributes of the RAM as indicated below. The register is then placed between the TDI and TDO pins when the

controller is moved into Shift-DR state. Bit 0 in the register is the LSB and the first to reach TDO when shifting begins.

Instruction Register

ID Code Register

Boundary Scan Register

0

1

2

0

31 30 29

1

2

0

Bypass Register

TDI

TDO

TMS

TCK

Test Access Port (TAP) Controller

108

1

0

Control Signals

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GS816032T-250T | 512K X 32 CACHE SRAM, 5.5 ns, PQFP100 |

| GS816036BGT-300 | 512K X 36 CACHE SRAM, 5.3 ns, PQFP100 |

| GS816037T-133I | 512K X 36 CACHE SRAM, 3.5 ns, PQFP100 |

| GS8160E18AT-300 | 1M X 18 CACHE SRAM, 5 ns, PQFP100 |

| GS8160V18AGT-150IT | 1M X 18 CACHE SRAM, 7.5 ns, PQFP100 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GS8150V36AB-333 | 制造商:GSI Technology 功能描述:GS8150V36AB-333 - Trays |

| GS8150V36AB-333I | 制造商:GSI 制造商全稱:GSI Technology 功能描述:1M x 18, 512K x 36 18Mb Register-Register Late Write SRAM |

| GS8150V36AB-357 | 制造商:GSI Technology 功能描述:GS8150V36AB-357 - Trays |

| GS8150V36AB-357I | 制造商:GSI 制造商全稱:GSI Technology 功能描述:1M x 18, 512K x 36 18Mb Register-Register Late Write SRAM |

| GS8150V36AGB-250 | 制造商:GSI 制造商全稱:GSI Technology 功能描述:1M x 18, 512K x 36 18Mb Register-Register Late Write SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。