- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370744 > HYB 39S128400CT (SIEMENS AG) 128-Mbit(4banks × 8MBit × 4) Synchronous DRAM(128M(4列 × 8M位 × 4)同步動(dòng)態(tài)RAM) PDF資料下載

參數(shù)資料

| 型號(hào): | HYB 39S128400CT |

| 廠商: | SIEMENS AG |

| 英文描述: | 128-Mbit(4banks × 8MBit × 4) Synchronous DRAM(128M(4列 × 8M位 × 4)同步動(dòng)態(tài)RAM) |

| 中文描述: | 128兆位(4banks × 8MBit × 4)同步DRAM(128M的(4列× 800萬(wàn)位× 4)同步動(dòng)態(tài)RAM)的 |

| 文件頁(yè)數(shù): | 12/42頁(yè) |

| 文件大?。?/td> | 280K |

| 代理商: | HYB 39S128400CT |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)

HYB 39S128400/800/160CT(L)

128-MBit Synchronous DRAM

Data Book

12

1.00

done even before the previous burst ends. The interrupt operation at every clock cycle is supported.

When the previous burst is interrupted, the remaining addresses are overridden by the new address

with the full burst length. An interrupt which accompanies an operation change from a read to a write

is possible by exploiting DQM to avoid bus contention.

When two or more banks are activated sequentially, interleaved bank read or write operations are

possible. With the programmed burst length, alternate access and precharge operations on two or

more banks can realize fast serial data access modes among many different pages. Once two or

more banks are activated, column to column interleave operation can be performed between

different pages.

Refresh Mode

SDRAM has two refresh modes, Auto Refresh and Self Refresh. Auto Refresh is similar to the CAS

-before-RAS refresh of conventional DRAMs. All of banks must be precharged before applying any

refresh mode. An on-chip address counter increments the word and the bank addresses and no

bank information is required for both refresh modes.

The chip enters the Auto Refresh mode, when RAS and CAS are held low and CKE and WE are

held high at a clock timing. The mode restores word line after the refresh and no external precharge

command is necessary. A minimum

t

RC

time is required between two automatic refreshes in a burst

refresh mode. The same rule applies to any access command after the automatic refresh operation.

The chip has an on-chip timer and the Self Refresh mode is available. It enters the mode when RAS,

CAS, and CKE are low and WE is high at a clock timing. All of external control signals including the

clock are disabled. Returning CKE to high enables the clock and initiates the refresh exit operation.

After the exit command, at least one

t

RC

delay is required prior to any access command.

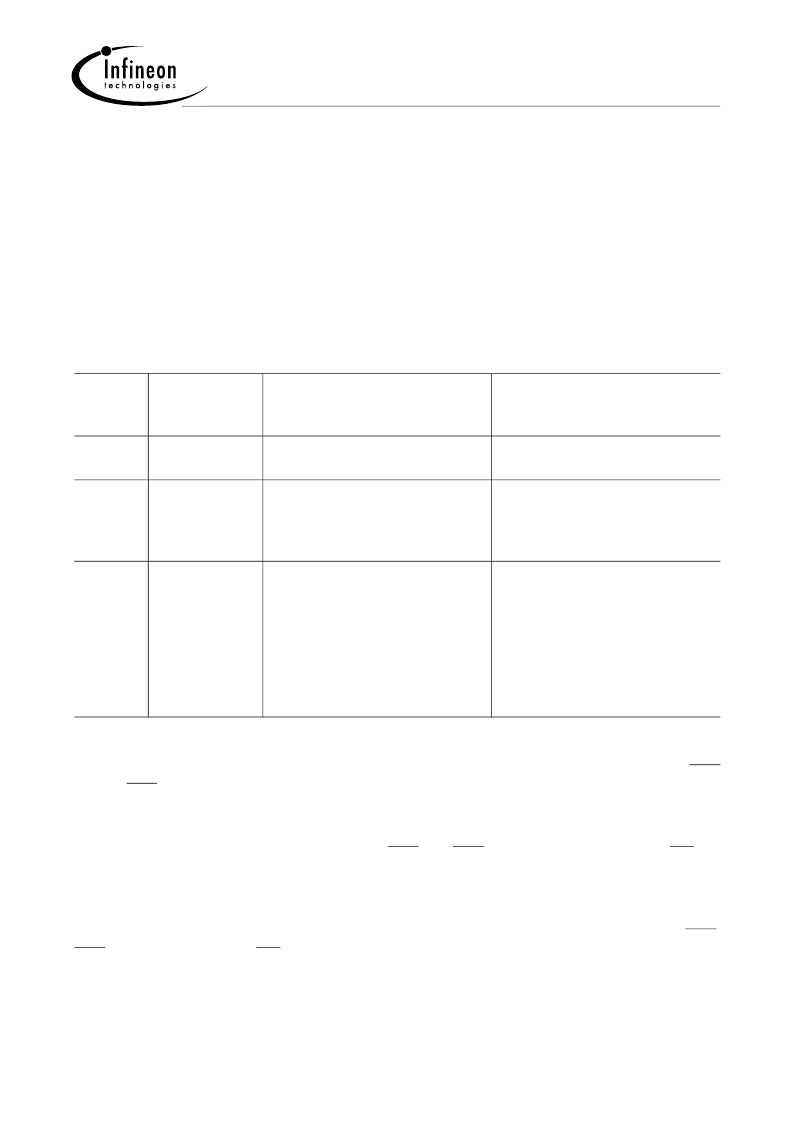

Burst Length and Sequence

Burst

Length

Starting

Address

(A2 A1 A0)

Sequential Burst

Addressing

(decimal)

Interleave Burst

Addressing

(decimal)

2

xx0

xx1

0, 1

1, 0

0, 1

1, 0

4

x00

x01

x10

x11

0, 1, 2, 3

1, 2, 3, 0

2, 3, 0, 1

3, 0, 1, 2

0, 1, 2, 3

1, 0, 3, 2

2, 3, 0, 1

3, 2, 1, 0

8

000

001

010

011

100

101

110

111

0 1 2 3 4 5 6 7

1 2 3 4 5 6 7 0

2 3 4 5 6 7 0 1

3 4 5 6 7 0 1 2

4 5 6 7 0 1 2 3

5 6 7 0 1 2 3 4

6 7 0 1 2 3 4 5

7 0 1 2 3 4 5 6

0 1 2 3 4 5 6 7

1 0 3 2 5 4 7 6

2 3 0 1 6 7 4 5

3 2 1 0 7 6 5 4

4 5 6 7 0 1 2 3

5 4 7 6 1 0 3 2

6 7 4 5 2 3 0 1

7 6 5 4 3 2 1 0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYB 39S128800CT | 128-Mbit(4banks × 4MBit × 8) Synchronous DRAM(128M(4列 × 4M位 × 8)同步動(dòng)態(tài)RAM) |

| HYB 39S16160CT-5.5 | 1M × 16-Mbit Synchronous DRAM for High-Speed Graphics Applications(16M位(1M × 16)同步動(dòng)態(tài)RAM(用于高速圖形場(chǎng)合)) |

| HYB 39S16160CT-6 | 1M × 16-Mbit Synchronous DRAM for High-Speed Graphics Applications(16M位(1M × 16)同步動(dòng)態(tài)RAM(用于高速圖形場(chǎng)合)) |

| HYB 39S16160CT-7 | 1M × 16-Mbit Synchronous DRAM for High-Speed Graphics Applications(16M位(1M × 16)同步動(dòng)態(tài)RAM(用于高速圖形場(chǎng)合)) |

| HYB 39S256160T | 256-Mbit(4banks × 4MBit × 16) Synchronous DRAM(256M(4列 × 4M位 × 16)同步動(dòng)態(tài)RAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYB39S128400CT-7 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128-MBit Synchronous DRAM |

| HYB39S128400CT-7.5 | 制造商:Infineon Technologies AG 功能描述:32M X 4 SYNCHRONOUS DRAM, 5.4 NS, PDSO54 |

| HYB39S128400CT-75 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128-MBit Synchronous DRAM |

| HYB39S128400CT-8 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128-MBit Synchronous DRAM |

| HYB39S128400F | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:128-MBit Synchronous DRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。