- 您現在的位置:買賣IC網 > PDF目錄224008 > ICSSSTUAF32868BHLFT (INTEGRATED DEVICE TECHNOLOGY INC) 32868 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA176 PDF資料下載

參數資料

| 型號: | ICSSSTUAF32868BHLFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 鎖存器 |

| 英文描述: | 32868 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA176 |

| 封裝: | LEAD FREE, MO-205/MO-255/MO-246, LFBGA-176 |

| 文件頁數: | 6/22頁 |

| 文件大小: | 538K |

| 代理商: | ICSSSTUAF32868BHLFT |

ICSSSTUAF32868B

28-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2

COMMERCIAL TEMPERATURE GRADE

28-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2

14

ICSSSTUAF32868B

7102/2

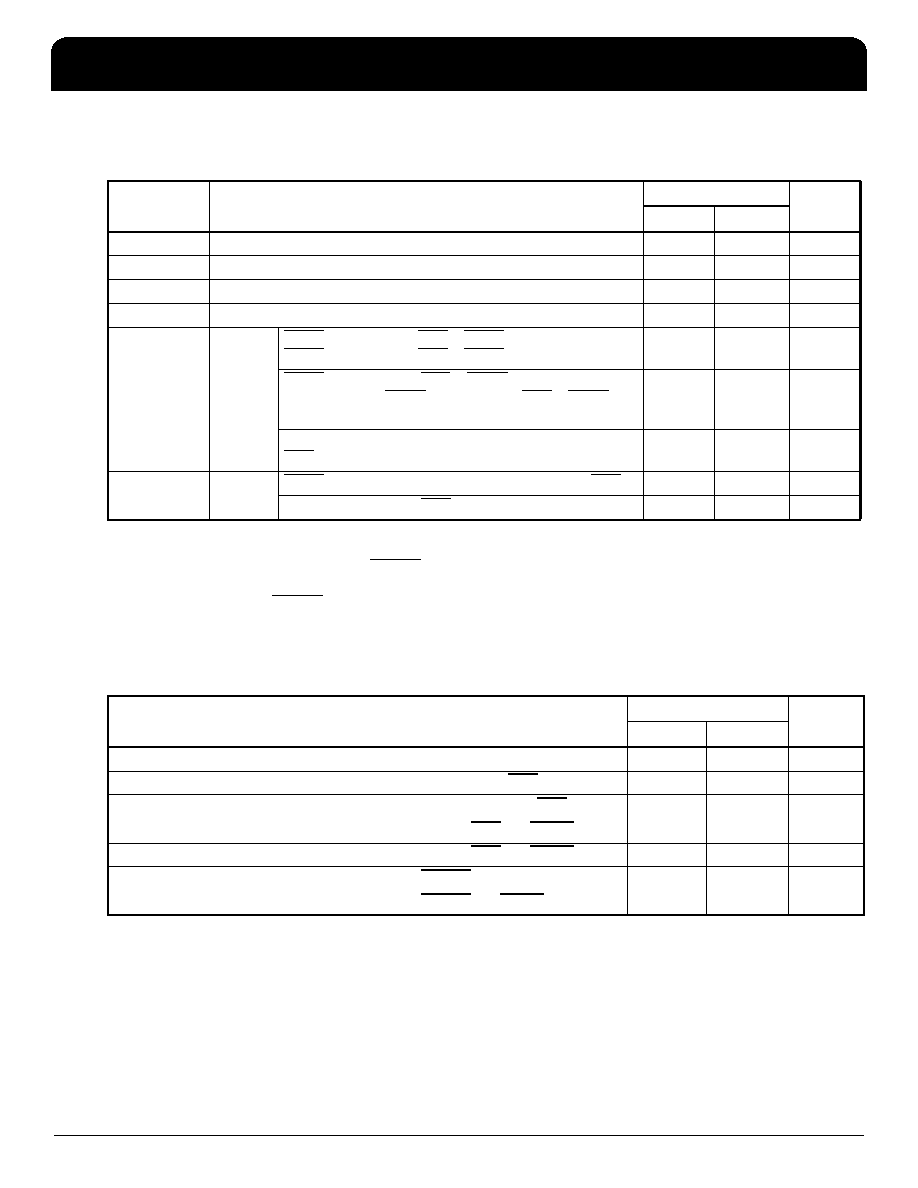

Timing Requirements Over Recommended Operating Free-Air Temperature

Range

Switching Characteristics Over Recommended Free Air Operating Range

(unless otherwise noted)

Symbol

Parameter

VDD = 1.8V ± 0.1V

Units

Min.

Max.

fCLOCK

Clock Frequency

410

MHz

tW

Pulse Duration, CLK, CLK HIGH or LOW

1

ns

tACT1,2

1

This parameter is not production tested.

2

VREF must be held at a valid input voltage level and data inputs must be held at valid voltage levels for

a minimum time of tACT (max) after RESET is taken HIGH.

Differential Inputs Active Time

10

ns

3

VREF data and clock inputs must be held at valid input voltage levels (not floating) for a minimum time

of tINACT (max) after RESET is taken LOW.

Differential Inputs Inactive Time

15

ns

tSU

Setup

Time

DCS0 before CLK

↑, CLK↓, DCS1 and CSGEN HIGH;

DCS1 before CLK

↑, CLK↓, DCS0 and CSGEN HIGH;

0.7

ns

DCS0 before CLK

↑, CLK↓, DCS1 LOW and CSGEN

HIGH or LOW; DCS1 before CLK

↑, CLK↓, DCS0

LOW and CSGEN HIGH or LOW

0.5

ns

DODTn, DCKEn, PAR_IN, and data before CLK

↑,

CLK

↓

0.5

ns

tH

Hold

Time

DCSn, DODT,n DCKEn, and data after CLK

↑, CLK↓

0.5

ns

PAR_IN after CLK

↑, CLK↓

0.5

ns

Symbol

Parameter

VDD = 1.8V ± 0.1V

Units

Min.

Max.

fMAX

Max Input Clock Frequency

410

MHz

tPDM

Propagation Delay, single bit switching, CLK

↑ / CLK↓ to Qn

1.3

1.9

ns

tPDMSS

Propagation Delay, simultaneous switching, CLK

↑ / CLK↓ to Qn

2

ns

tLH

LOW to HIGH Propagation Delay, CLK

↑ / CLK↓ to QERR

0.9

3

ns

tHL

HIGH to LOW Propagation Delay, CLK

↑ / CLK↓ to QERR

0.7

2.4

ns

tPLH

HIGH to LOW Propagation Delay, RESET

↓ to Qn↓

3ns

tPHL

LOW to HIGH Propagation Delay, RESET

↓ to QERR↑

3ns

相關PDF資料 |

PDF描述 |

|---|---|

| IDT2309-1HDCGI8 | PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| IDT54FCT373CTEB | FCT SERIES, 8-BIT DRIVER, TRUE OUTPUT, CDFP20 |

| IDT5V996BBI | 5V SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 |

| IDT5V996BBI8 | 5V SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 |

| IDT71258L35TP | 64K X 4 STANDARD SRAM, 35 ns, PDIP24 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ICSSSTUAF32869A | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:14-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

| ICSSSTUAF32869AHLF | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:14-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

| ICSSSTUAH32865A | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

| ICSSSTUAH32865AHLFT | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

| ICSSSTUAH32868A | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:28-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

發(fā)布緊急采購,3分鐘左右您將得到回復。