- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄377397 > IDT72103L35J (INTEGRATED DEVICE TECHNOLOGY INC) CMOS PARALLEL-SERIAL FIFO 2048 x 9, 4096 x 9 PDF資料下載

參數(shù)資料

| 型號(hào): | IDT72103L35J |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類(lèi): | DRAM |

| 英文描述: | CMOS PARALLEL-SERIAL FIFO 2048 x 9, 4096 x 9 |

| 中文描述: | 2K X 9 OTHER FIFO, 35 ns, PQCC44 |

| 封裝: | PLASTIC, LCC-44 |

| 文件頁(yè)數(shù): | 20/31頁(yè) |

| 文件大?。?/td> | 314K |

| 代理商: | IDT72103L35J |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)

5.37

20

IDT72103, IDT72104

CMOS PARALLEL-SERIAL FIFO 2048 x 9, 4096 x 9

COMMERCIAL TEMPERATURE RANGES

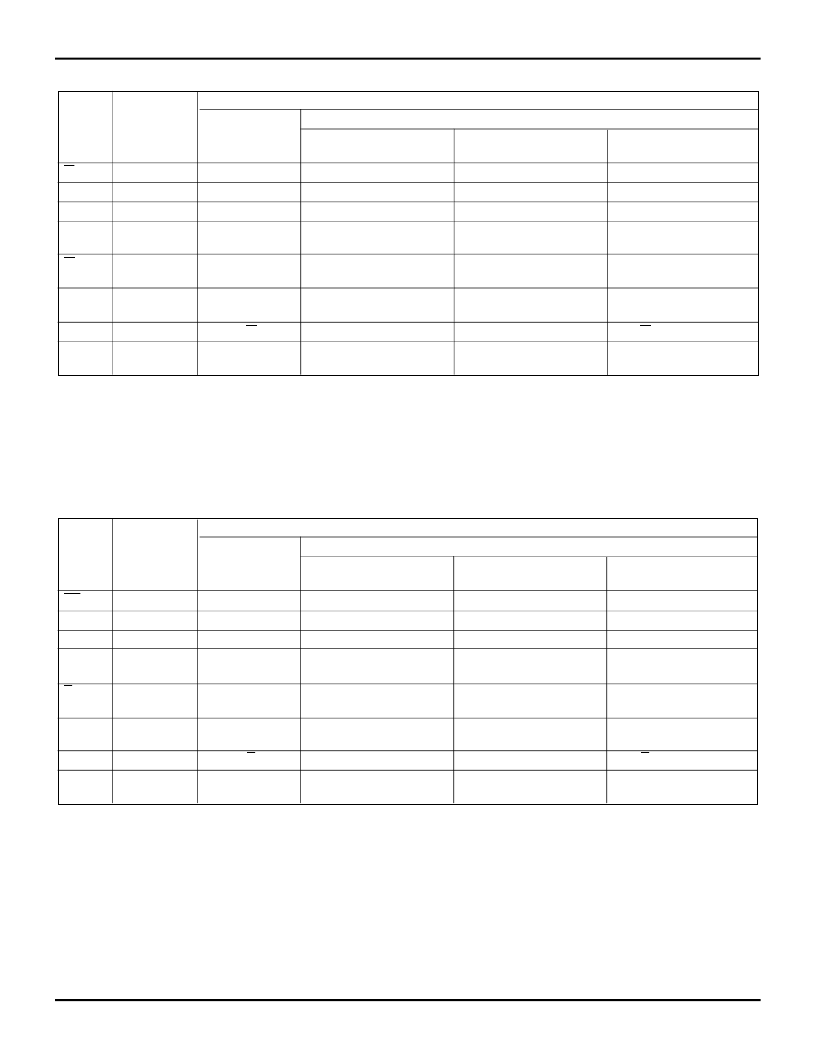

INPUT CONFIGURATION TABLE

Serial Input

Width Expansion

All Other

Devices

LOW

Input Data

Input Clock

Parallel

Input

HIGH

HIGH or LOW

HIGH or LOW

Single

Device

LOW

Input Data

Input Clock

Least Significant

Device

LOW

Input Data

Input Clock

Most Significant

Device

LOW

Input Data

Input Clock

Pin

SI

/PI

Sl

SICP

SIX

HIGH

HIGH

HIGH

D

8

of next least

significant device

Di of most

significant device

No connect except D

8

D

of next least

significant device

Di of most

significant device

No connect except Di

W

Write Control

Di

Di of most

significant device

No connect except D

8

D

0

-D

8

Input Data

No connect

except Di

W

Di

D

8

(1)

—

—

—

—

W

of all devices

—

—

SIX of next most

significant device

SIX of next most

significant device

NOTE:

1. Di refers to the rnost significant bit of the serial word. If multiple devices are width cascaded, Di is the rnost significant bit from the most

significant device.

2753 tbl 11

OUTPUT CONFIGURATION TABLE

Serial Output

Width Expansion

All Other

Devices

LOW

Output Data

Output Clock

Q

of next least

significant device

Qi of most

significant device

No connect except Q

8

Parallel

Output

HIGH

—

HIGH or LOW

HIGH

Single

Device

LOW

Output Data

Output Clock

HIGH

Least Significant

Device

LOW

Output Data

Output Clock

HIGH

Most Significant

Device

LOW

Output Data

Output Clock

Q

of next least

significant device

Qi of most

significant device

No connect except Qi

Pin

SO

/PO

SO

SOCP

SOX

R

Read Control

Qi

Qi of most

significant device

No connect except Q

8

Q

0

-Q

8

Output Data

No connect

except Di

R

Qi

Q

8

(1)

—

—

—

—

R

of all devices

—

—

SOX of next most

significant device

SOX of next most

significant device

NOTE:

1. Qi refers to the most significant bit of the serial word. If multiple devices are width cascaded, Qi is the rnost significant bit from the most

significant device.

2753 tbl 12

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT72103L50J | CMOS PARALLEL-SERIAL FIFO 2048 x 9, 4096 x 9 |

| IDT72104L50J | CMOS PARALLEL-SERIAL FIFO 2048 x 9, 4096 x 9 |

| IDT72105 | CMOS PARALLEL-TO-SERIAL FIFO 256 x 16, 512 x 16, 1024 x 16 |

| IDT72105L25SO | Current-Mode PWM Controller 14-SOIC -40 to 85 |

| IDT72105L25TP | Current-Mode PWM Controller 8-SOIC -40 to 85 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72103S50P | 制造商:Integrated Device Technology Inc 功能描述: |

| IDT72104S120P | 制造商:Integrated Device Technology Inc 功能描述: |

| IDT72104S50D | 制造商:Integrated Device Technology Inc 功能描述: 制造商:Integrated Device Technology Inc 功能描述:4K X 9 OTHER FIFO, 50 ns, CDIP40 |

| IDT72104S50P | 制造商:IDT/89'S 功能描述:FIFO, 4K x 9, Asynchronous, 40 Pin, Plastic, DIP |

| IDT72105L50S0 | 制造商:Integrated Device Technology Inc 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。