- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45377 > IF180C52EXXX-L16:R (TEMIC SEMICONDUCTORS) 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP44 PDF資料下載

參數(shù)資料

| 型號: | IF180C52EXXX-L16:R |

| 廠商: | TEMIC SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP44 |

| 文件頁數(shù): | 6/101頁 |

| 文件大小: | 3398K |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁

AT86RF212

(parameter 10.4.12). During reset, the microcontroller has to set the radio transceiver

control pins SLP_TR and /SEL to their default values.

An overview of the register reset values is provided in Table 11-2.

5.1.3 Interrupt Handling

All interrupts provided by the AT86RF212 (see Table 4-15) are supported in Basic

Operating Mode. For example, interrupts are provided to observe the status of radio

transceiver RX and TX operations.

When being in receive mode, IRQ_2 (RX_START) indicates the detection of a non-zero

PHR first, IRQ_5 (AMI) an address match, and IRQ_3 (TRX_END) the completion of

the frame reception. During transmission, IRQ_3 (TRX_END) indicates the completion

of the frame transmission.

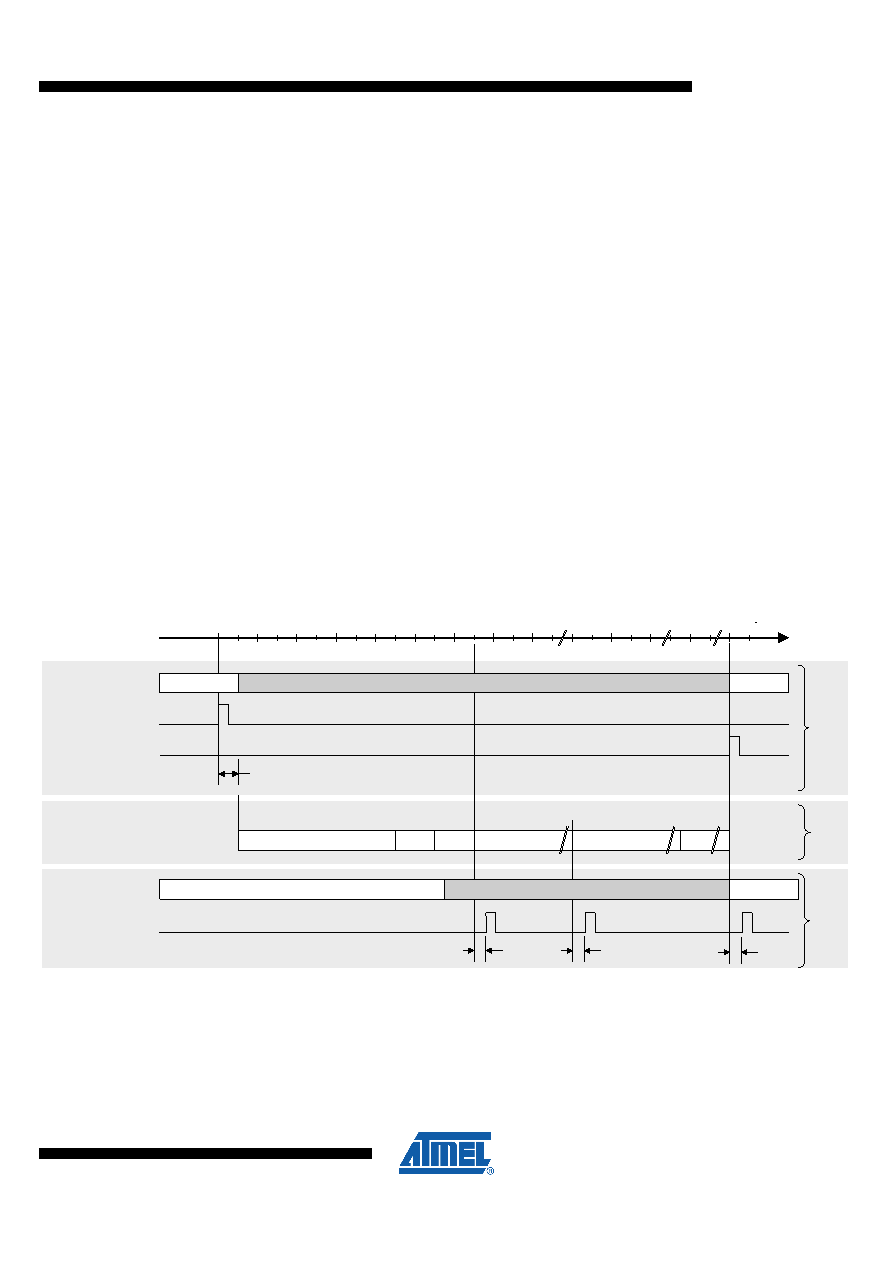

Figure 5-2 shows an example for a transmit/receive transaction between two devices

and the related interrupt events in Basic Operating Mode. Device 1 transmits a frame

containing a MAC header, MAC payload, and a valid FCS. The end of the frame

transmission is indicated by IRQ_3 (TRX_END).

The frame is received by Device 2. Interrupt IRQ_2 (RX_START) indicates the

detection of a valid PHR field and IRQ_3 (TRX_END) the completion of the frame

reception. If the frame passes the Frame Filter (refer to 6.2), an address match interrupt

IRQ_5 (AMI) is issued after the reception of the MAC header (MHR).

Figure 5-2. Timing of RX_START, AMI, and TRX_END Interrupts in Basic Operating Mode for O-QPSK 250 kbit/s Mode

128

160

192

0

192+(m+n+2) 32 Time [μs]

RX

(De

vic

e2)

IRQ_2 (RX_START)

tIRQ

RX_ON

IRQ

State

Interrupt latency

TRX_END

IRQ_5 (AMI)

tIRQ

BUSY_RX

IRQ_3 (TRX_END)

TX

(D

ev

ic

e1

)

PLL_ON

BUSY_TX

PLL_ON

IRQ

SLP_TR

State

Processing Delay

Fra

m

e

on

A

ir

Preamble

SFD

PHR

MSDU

41

1

m

Number of Octets

Frame Content

MHR

FCS

2

tTR10

-tTR10

n

5.1.4 Timing

The following paragraphs depict state transitions and their timing properties. Timings

35

8168C-MCU Wireless-02/10

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MQ80C52CXXX-20/883R | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CQFP44 |

| MJ80C31U-36:D | MICROCONTROLLER |

| R80C52XXX-12SHXXX | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CQCC44 |

| MQ80C32-12SBR | 8-BIT, 12 MHz, MICROCONTROLLER, CQFP44 |

| IF180C52XXX-36D | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, PQFP44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IF180C52-L16 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| IF180C52T-12 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| IF180C52T-16 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| IF180C52T-20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| IF180C52T-25 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。