- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377496 > INTEL82802AB (Intel Corp.) Firmware Hub (FWH) PDF資料下載

參數(shù)資料

| 型號(hào): | INTEL82802AB |

| 廠商: | Intel Corp. |

| 英文描述: | Firmware Hub (FWH) |

| 中文描述: | 固件集線器(固件樞紐) |

| 文件頁數(shù): | 44/53頁 |

| 文件大小: | 471K |

| 代理商: | INTEL82802AB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁當(dāng)前第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁

Intel

82802AB/AC Firmware Hub

R

44

Datasheet

5.4.1.6.

Abort Operations

FWH4 active (low) indicates either that a START cycle will eventually occur or that an abort is in

progress. In either case, if FWH4 is asserted, the Intel FWH will “immediately” tri-state its outputs and

the FWH state machine will reset.

During a write cycle, there is a possibility that an internal flash write or erase operation is in progress (or

has just been initiated). If FWH4 is asserted during this time frame, the internal operation will

not

abort.

The software must send an explicit flash command to terminate or suspend the operation.

The internal FWH state machine will not initiate a flash write or erase operation until it has received the

last data nibble from the chipset. This means that FWH4 can be asserted as late as this cycle (“cycle 12”)

and no internal flash operation will be attempted. However, since the Intel FWH will start “processing”

incoming data before it generates its SYNC field, it should be considered a

non-buffered peripheral

device.

5.4.1.7.

Intel FWH Cycle Timing Information

Refer to Figure Figure 12 and Figure 13.

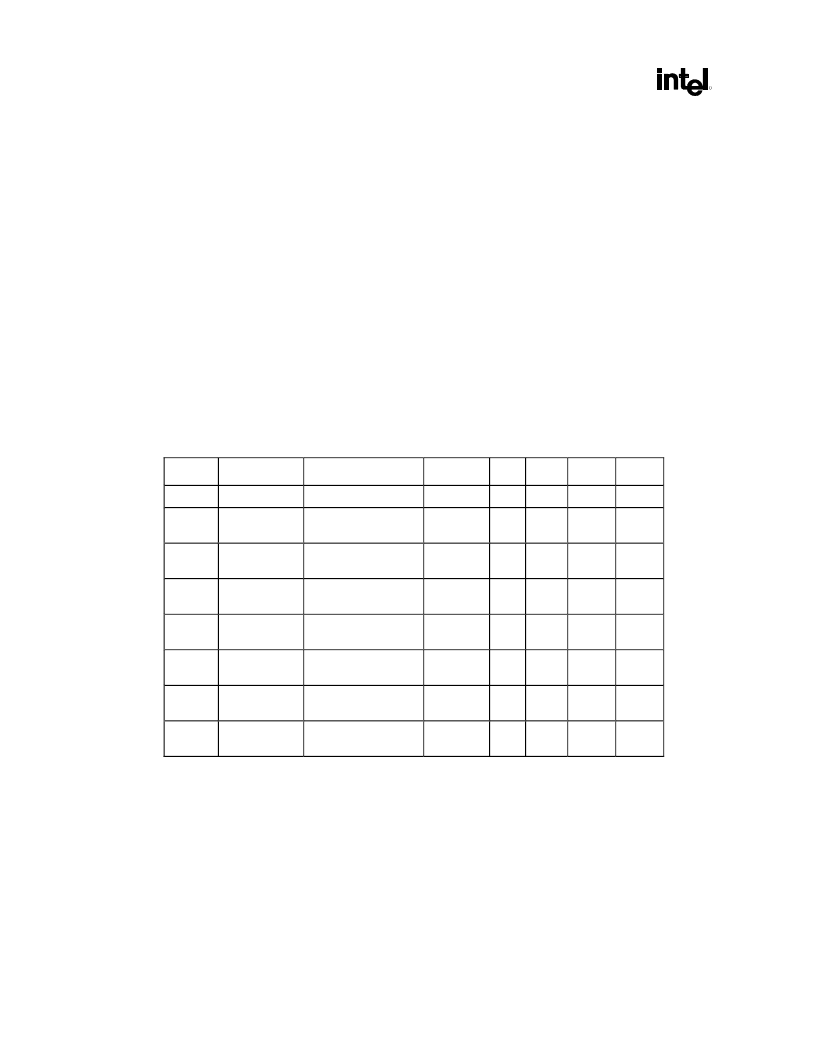

Table 18.

Signal Timing Parameters

Symbol

“PCI Symbol”

Parameter

Condition

Min.

Max.

Units

Notes

TCHQV

t

val

CLK to data out

2

11

ns

1

TCHQX

t

on

CLK to active

(float to active delay)

2

ns

2

TCHQZ

t

off

CLK to inactive

(active to float delay)

28

ns

2

TAVCH

TDVCH

t

su

Input setup time

7

ns

3

TCHAX

TCHDX

t

h

Input hold time

0

ns

3

TVSPL

t

rst

Reset active time after

power stable

1

ms

TCSPL

t

rst-clk

Reset active time after

CLK stable

100

μ

s

TPLQZ

t

rst-off

Reset active to output

float delay

48

ns

2

Note:

1. Minimum and maximum times have different loads. See the PCI specification.

2. For purposes of active/float timing measurements, the Hi-Z or “off” state is defined as the state

where the total current delivered through the component pin is less than or equal to the leakage

current specification.

3. This parameter applies to any input type (excluding CLK).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| INTELDX2 | High-Performance 32-Bit Embedded Processor(高性能32位嵌入式處理器) |

| INTELDX4 | Embedded Write-Back Enhanced Processor(32位回復(fù)嵌入式增強(qiáng)型處理器) |

| IPS54511 | FULLY PROTECTED HIGH SIDE POWER MOSFET SWITCH |

| IPS5451 | FULLY PROTECTED HIGH SIDE POWER MOSFET SWITCH |

| IPS5451S | FULLY PROTECTED HIGH SIDE POWER MOSFET SWITCH |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| INTELLIGENT CHARGER + 4AA | 制造商:Energizer 功能描述:Bulk |

| INTELLI-INCH-LR-STARTER K | 制造商:ALL MOTION 功能描述:Intelli-Inch Stepper & Controller Starter Kit |

| INTELLIPANEL | 制造商:GJD 功能描述:EXTENSION LEAD 8GANG INTELLIPANEL 制造商:GJD 功能描述:EXTENSION LEAD, 8GANG, INTELLIPANEL |

| INTELLIPLUG | 制造商:GLOBAL COMMUNICATIONS 功能描述:ADAPTOR 3WAY INTELLIPLUG |

| INTELLIPROBE 100 | 制造商:Fluke Networks 功能描述:TONE + PROBE KIT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。