- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1925 > IS80C286-20 (Intersil)IC CPU 16BIT 5V 20MHZ 68-PLCC PDF資料下載

參數(shù)資料

| 型號: | IS80C286-20 |

| 廠商: | Intersil |

| 文件頁數(shù): | 9/60頁 |

| 文件大小: | 0K |

| 描述: | IC CPU 16BIT 5V 20MHZ 68-PLCC |

| 標(biāo)準(zhǔn)包裝: | 18 |

| 處理器類型: | 80C286 16-位 |

| 速度: | 20MHz |

| 電壓: | 5V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 68-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 68-PLCC(24.23x24.23) |

| 包裝: | 管件 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

17

Protected Virtual Address Mode

The 80C286 executes a fully upward-compatible superset of

the 80C86 instruction set in protected virtual address mode

(protected mode). Protected mode also provides memory

management and protection mechanisms and associated

instructions.

The 80C286 enters protected virtual address mode from real

address mode by setting the PE (Protection Enable) bit of

the machine status word with the Load Machine Status Word

(LMSW) instruction. Protected mode offers extended physi-

cal and virtual memory address space, memory protection

mechanisms, and new operations to support operating sys-

tems and virtual memory.

All registers, instructions, and addressing modes described

in the 80C286 Base Architecture section of this Functional

Description remain the same. Programs for the 80C86,

80C88, and real address mode 80C286 can be run in pro-

tected mode; however, embedded constants for segment

selectors are different.

Memory Size

The protected mode 80C286 provides a 1 gigabyte virtual

address space per task mapped into a 16 megabyte physical

address space defined by the address pins A23-A0 and

BHE. The virtual address space may be larger than the

physical address space since any use of an address that

does not map to a physical memory location will cause a

restartable exception.

Memory Addressing

As in real address mode, protected mode uses 32-bit point-

ers, consisting of 16-bit selector and offset components. The

selector, however, specifies an index into a memory resident

table rather than the upper 16-bits of a real memory address.

The 24-bit base address of the desired segment is obtained

from the tables in memory. The 16-bit offset is added to the

segment base address to form the physical address as

shown in Figure 8. The tables are automatically referenced

by the CPU whenever a segment register is loaded with a

selector. All 80C286 instructions which load a segment reg-

ister will reference the memory based tables without addi-

tional software. The memory based tables contain 8 byte

values called descriptors.

Descriptors

Descriptors define the use of memory. Special types of

descriptors also define new functions for transfer of control

and task switching. The 80C286 has segment descriptors for

code, stack and data segments, and system control descrip-

tors for special system data segments and control transfer

operations. Descriptor accesses are performed as locked

bus operations to assure descriptor integrity in multi-proces-

sor systems.

Code and Data Segment Descriptors (S = 1)

Besides segment base addresses, code and data descriptors

contain other segment attributes including segment size (1 to

64K bytes), access rights (read only, read/write, execute only,

and execute/read), and presence in memory (for virtual mem-

ory systems) (See Table 10). Any segment usage violating a

segment attribute indicated by the segment descriptor will pre-

vent the memory cycle and cause an exception or interrupt.

Code and data (including stack data) are stored in two types

of segments: code segments and data segments. Both types

are identified and defined by segment descriptors (S = 1).

Code segments are identified by the executable (E) bit set to

1 in the descriptor access rights byte. The access rights byte

of both code and data segment descriptor types have three

fields in common: present (P) bit, Descriptor Privilege Level

(DPL), and accessed (A) bit. If P = 0, any attempted use of

this segment will cause a not-present exception. DPL speci-

fies the privilege level of the segment descriptor. DPL con-

trols when the descriptor may be used by a task (refer to

privilege discussion below). The A bit shows whether the

segment has been previously accessed for usage profiling, a

necessity for virtual memory systems. The CPU will always

set this bit when accessing the descriptor.

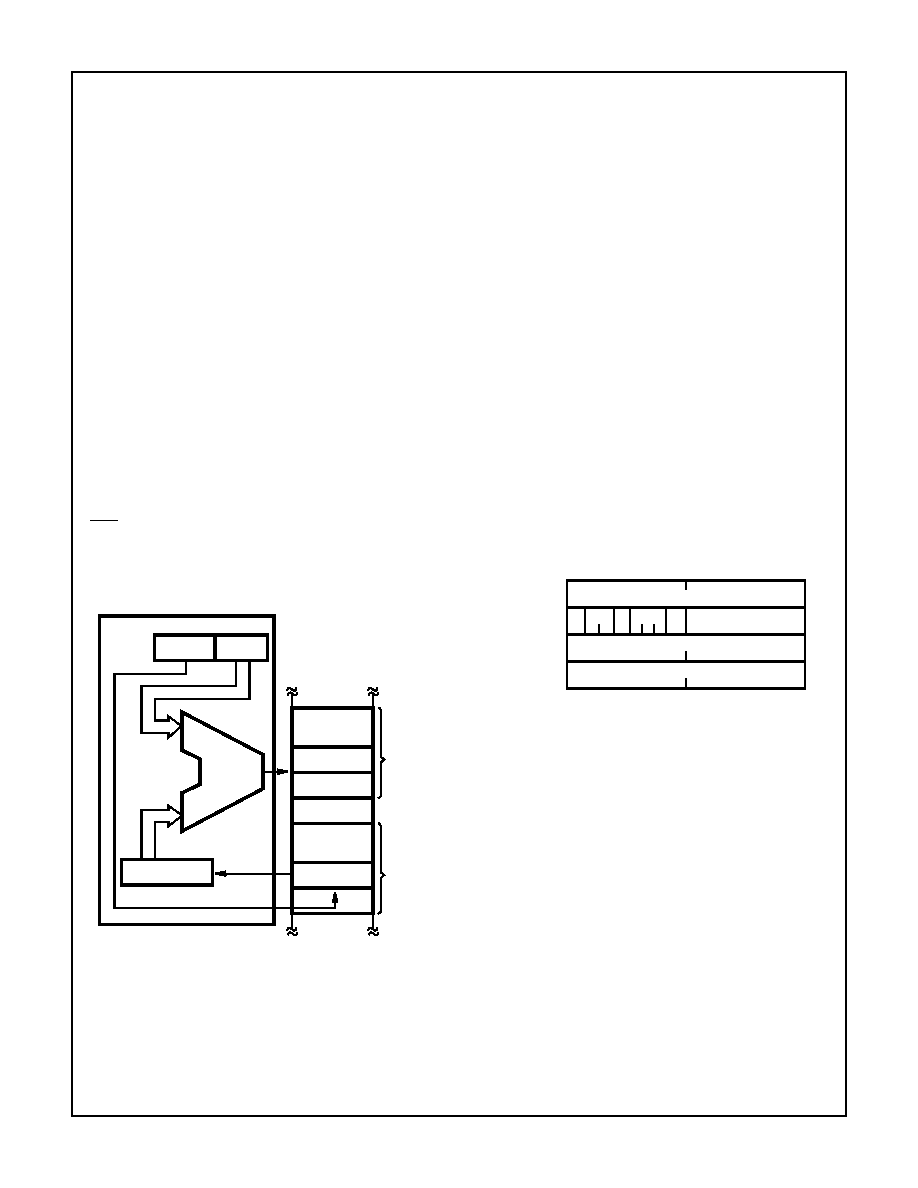

PHYSICAL

ADDRESS

ADDER

MEMORY

OPERAND

SEGMENT

DESCRIPTOR

SEGMENT BASE

ADDRESS

POINTER SELECTOR OFFSET

PHYSICAL MEMORY

SEGMENT

SEG

MENT

DESCRIPTION

TABL

E

0

23

31

16 15

0

CPU

FIGURE 8. PROTECTED MODE MEMORY ADDRESSING

RESERVED

ACCESS

RIGHTS BYTE

PDPL STYPE A

BASE 23 - 16

BASE 15 - 0

LIMIT 15 - 0

15

70 7

7

80

0

+6

+4

+2

0

+7

+5

+3

+1

MUST BE SET TO 0 FOR COMPATIBILITY WITH FUTURE UPGRADES

FIGURE 9. CODE OR DATA SEGMENT DESCRIPTOR

80C286

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISL1532IRZ | IC LINE DRIVER DUAL 24-QFN |

| ISL1536IRZ | IC LINE DRVR DUAL ADSL2+ 16-QFN |

| ISL1539AIRZ | IC VDSL2 LINE DVR AMP 24QFN |

| ISL1539IVEZ | IC VDSL2 LINE DVR AMP 24HTTSOP |

| ISL1557AIRZ | IC LINE DRIVER DUAL 16-QFN |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IS80C31 | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:CMOS SINGLE CHIP 8-BIT MICROCONTROLLER |

| IS80C31-12 | 制造商:TEMIC 功能描述:MicroController, 8-Bit, 44 Pin, Plastic, PLCC |

| IS80C31-12PL | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:CMOS SINGLE CHIP 8-BIT MICROCONTROLLER |

| IS80C31-12PLI | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:CMOS SINGLE CHIP 8-BIT MICROCONTROLLER |

| IS80C31-12PQ | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:CMOS SINGLE CHIP 8-BIT MICROCONTROLLER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。