- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄11593 > KSZ8842-PMBL (Micrel Inc)IC ETHERNT SW 2PORT PCI 100LFBGA PDF資料下載

參數(shù)資料

| 型號(hào): | KSZ8842-PMBL |

| 廠商: | Micrel Inc |

| 文件頁(yè)數(shù): | 52/119頁(yè) |

| 文件大小: | 0K |

| 描述: | IC ETHERNT SW 2PORT PCI 100LFBGA |

| 特色產(chǎn)品: | Micrel Drives Ethernet Into the Global Automotive World |

| 標(biāo)準(zhǔn)包裝: | 260 |

| 控制器類型: | 以太網(wǎng)開(kāi)關(guān)控制器 |

| 接口: | PCI |

| 電源電壓: | 3.1 V ~ 3.5 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-LFBGA |

| 供應(yīng)商設(shè)備封裝: | 100-LFBGA |

| 包裝: | 托盤 |

| 產(chǎn)品目錄頁(yè)面: | 1081 (CN2011-ZH PDF) |

| 配用: | 576-1636-ND - BOARD EVALUATION KSZ8842-PMQL |

| 其它名稱: | 576-3089 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)當(dāng)前第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)

Micrel, Inc.

KSZ8842-PMQL/PMBL

October 2007

38

M9999-100207-1.5

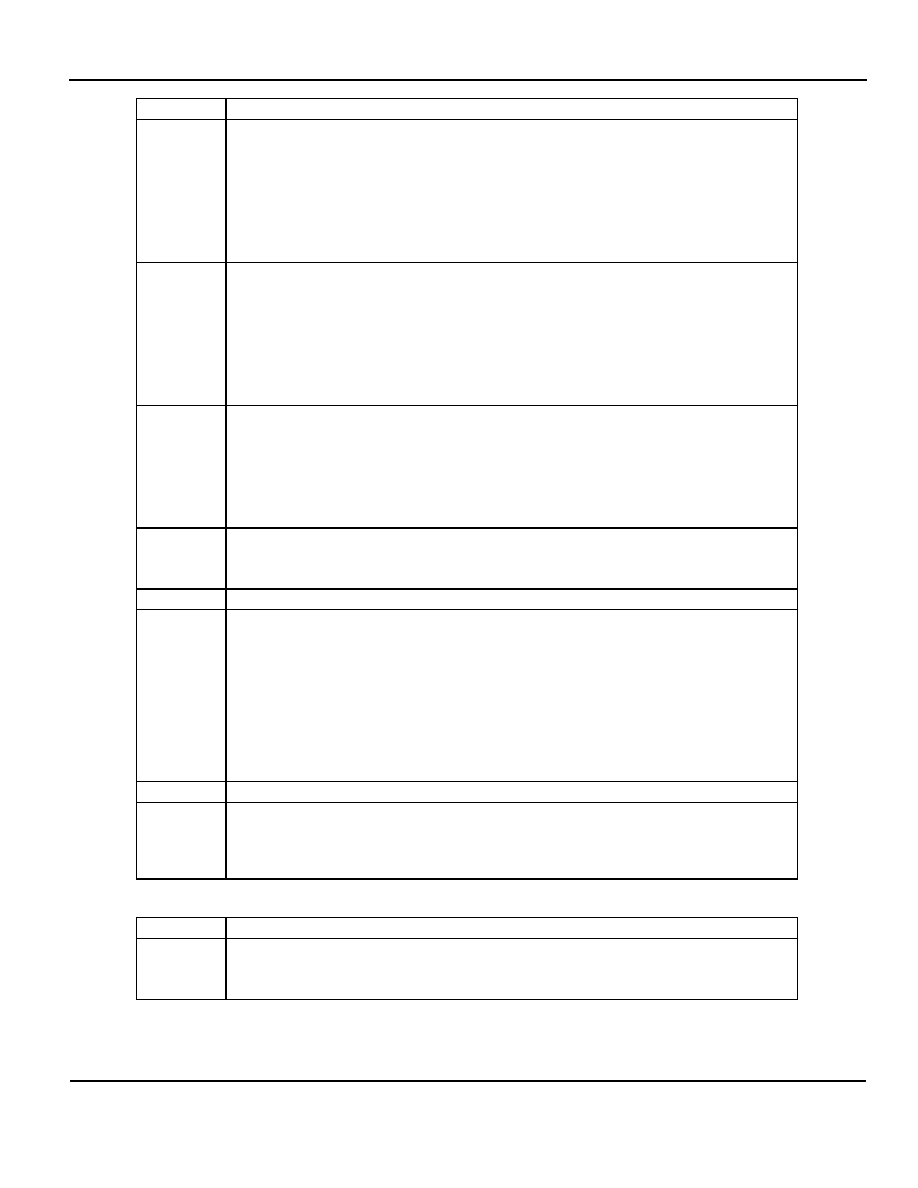

Bit

Description

28

IPCKG IP Checksum Generate

When set, the KSZ8842-PMQL/PMBL will generate correct IP checksum for outgoing frames

that contains IP protocol header. The KSZ8842-PMQL/PMBL supports only a standard IP

header, i.e., IP with a 20 byte header. When this feature is used, ADD CRC bit in the

transmit mode register should always be set.

This bit is used as a per-packet control when the IP checksum generate bit in the transmit

mode register is not set.

This bit should be always set for multiple-segment packets.

27

TCPCKG TCP Checksum Generate

When set, the KSZ8842-PMQL/PMBL will generate correct TCP checksum for outgoing

frames that contains IP and TCP protocol header. The KSZ8842-PMQL/PMBL supports only

a standard IP header, i.e., IP with a 20 byte header. When this feature is used, ADD CRC bit

in the transmit mode register should always be set.

This bit is used as a per-packet control when the TCP checksum generate bit in the transmit

mode register is not set.

This bit should be always set for multiple-segment packets.

26

UDPCKG UDP Checksum Generate

When set, the KSZ8842-PMQL/PMBL will generate correct UDP checksum for outgoing

frames that contains a IP and UDP protocol header. The KSZ8842-PMQL/PMBL supports

only a standard IP header, i.e., IP with a 20 byte header. When this feature is used, ADD

CRC bit in the transmit mode register should always be set.

This bit is used as a per-packet control when the UDP checksum generate bit in the transmit

mode register is not set.

25

TER Transmit End of Ring

When set, indicates that the descriptor pointer has reached its final descriptor.

The KSZ8842-PMQL/PMBL returns to the base address of the list, forming a descriptor ring.

24

Reserved

23 – 20

SPN Switch Engine Destination Port Map

When set, this field indicates the destination port(s) where the packet will be forwarded to.

If bit 20 is set, it indicates the packet was received from port 1. If bit 21 is set, it indicates the

packet was received from port 2.

Setting all ports to 1 will cause the switch engine to broadcast the packet.

Setting all bits to 0 has no effect. The switch engine forwards the packet according to its

internal switch lookup algorithm.

This field is valid only when the last descriptor is set.

(Bits 23 and 22 are not used, but reserved for backward compatibility and future expansion.)

19 – 11

Reserved

10 – 0

TBS Transmit Buffer Size

Indicates the size, in bytes, of the transmit data buffer.

If this field is 0, the KSZ8842-PMQL/PMBL ignores this buffer and moves to the next

descriptor.

The following table shows the TDES2 register bit fields.

Bit

Description

31 - 0

Buffer Address

Indicates the physical memory address of the buffer.

There is no limitation on the transmit buffer address alignment.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KSZ8893FQL-FX | IC SWITCH ETH 3PORT 128-PQFP |

| PIC12C509AT-04E/SN | IC MCU OTP 1KX12 8SOIC |

| PIC16F1829T-I/SS | MCU PIC 14K FLASH 1K RAM 20SSOP |

| V72A24C400BL3 | CONVERTER MOD DC/DC 24V 400W |

| PIC16F677-E/SS | IC PIC MCU FLASH 2KX14 20SSOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KSZ8842-PMBL AM | 功能描述:以太網(wǎng) IC 2-Port Ethernet Switch/Repeater + 32-bit/33MHz PCI bus interface(Lead Free) RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| KSZ8842-PMBL AM TR | 功能描述:以太網(wǎng) IC 2-Port Ethernet Switch/Repeater + 32-bit/33MHz PCI bus interface(Lead Free) RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| KSZ8842-PMBLAM | 制造商:Micrel 功能描述:Ethernet Switch 2-Port 10Mbps/100Mbps |

| KSZ8842-PMBL-AM | 功能描述:Ethernet Switch 10/100 Base-T/TX PHY PCI Interface 制造商:microchip technology 系列:- 包裝:托盤 零件狀態(tài):要求報(bào)價(jià) 協(xié)議:以太網(wǎng) 功能:開(kāi)關(guān) 接口:PCI 標(biāo)準(zhǔn):10/100 Base-T/TX PHY 電壓 - 電源:3.1 V ~ 3.5 V 電流 - 電源:122mA 工作溫度:-40°C ~ 85°C 封裝/外殼:100-LFBGA 供應(yīng)商器件封裝:* 標(biāo)準(zhǔn)包裝:260 |

| KSZ8842-PMBL-EVAL | 功能描述:以太網(wǎng)開(kāi)發(fā)工具 2+1 Port 10/100 Ethernet Switch with 32b/33MHz PCI Interface (BGA Version) Eval Board RoHS:否 制造商:Micrel 產(chǎn)品:Evaluation Boards 類型:Ethernet Transceivers 工具用于評(píng)估:KSZ8873RLL 接口類型:RMII 工作電源電壓: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。