- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄4594 > KSZ8995M (Micrel Inc)IC SWITCH 10/100 5PORT 128PQFP PDF資料下載

參數(shù)資料

| 型號(hào): | KSZ8995M |

| 廠(chǎng)商: | Micrel Inc |

| 文件頁(yè)數(shù): | 23/73頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC SWITCH 10/100 5PORT 128PQFP |

| 標(biāo)準(zhǔn)包裝: | 66 |

| 系列: | * |

| 類(lèi)型: | * |

| 應(yīng)用: | * |

| 安裝類(lèi)型: | 表面貼裝 |

| 封裝/外殼: | 128-BFQFP |

| 供應(yīng)商設(shè)備封裝: | 128-PQFP(14x20) |

| 包裝: | 托盤(pán) |

| 產(chǎn)品目錄頁(yè)面: | 1081 (CN2011-ZH PDF) |

| 配用: | 576-1607-ND - BOARD EVAL EXPERIMENT KSZ8995MA |

| 其它名稱(chēng): | 576-1038 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)當(dāng)前第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)

December 2003

3

M9999-120403

KS8995M

Micrel

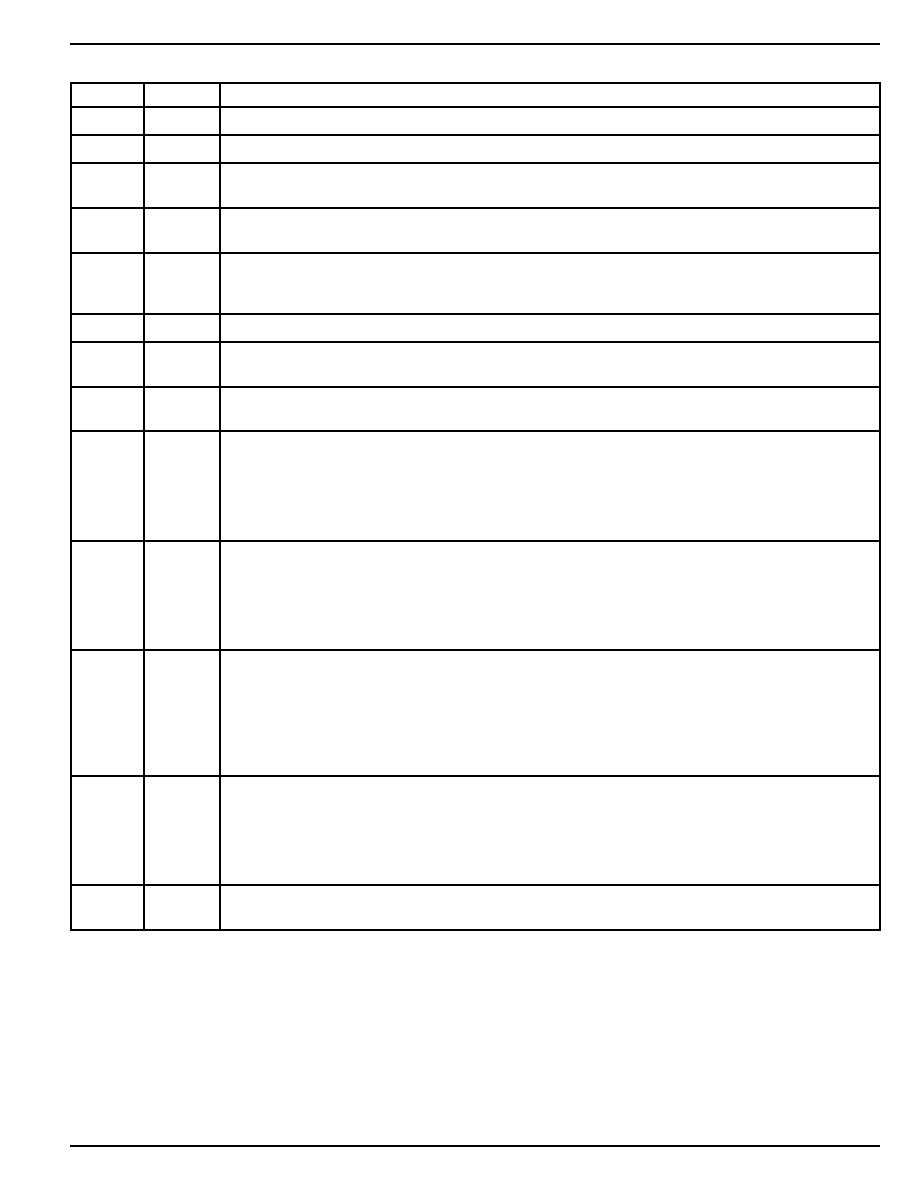

Revision History

Revision

Date

Summary of Changes

1.00

11/05/01

Created

1.01

11/09/01

Pinout Mux1/2, DVCC-IO 2.5/3.3V, feature list, register spec 11-09

1.02

12/03/01

Editorial changes, added new register and MIB descriptions. Added paragraph describing TOS registers.

Imported functional descriptions. Formatting.

1.03

12/12/01

Incorporate changes per engineering feedback as well as updating functional descriptions and adding

new timing information.

1.04

12/13/01

Changed Rev. and For. Modes to PHY and MAC modes respectively. Added MIIM clarification in “MII

Management Interface” section. Reformatted section sequence. Added hex register addresses. Added

advertisement ability descriptions.

1.05

12/18/01

Inserted switch forwarding flow charts.

1.06

12/20/01

Added new KS8995M block diagram, editorial changes, register descriptions changes and cross-

references from functional descriptions to register and strap in options.

1.07

1/22/01

Changed FXSD pins to inputs, added new descriptions to “Configuration Interfaces” section.

Edited pin descriptions.

1.08

3/1/02

Editorial changes in “Dynamic MAC Address table and “MIB Counters.” Updated figure 2 flowchart.

Updated table 2 for MAC mode connections. Separate static MAC bit assignments for read and write.

Edited read and write examples to MAC tables and MIB counters. Changed Table 3 KS8995M signals to

“S” suffix. Changed aging description in Register 2, bit 0. Changed “Port Registers” section and listed all

port register addresses. Changed port control 11 description for bits [7:5]. Changed MIB counter

descriptions.

1.09

5/17/02

Changed MII setting in “Pin Descriptions.” Changed pu/pd descriptions for SMRXD2. “Register 18,”

changed pu/pd description for forced flow control. “Illegal Frames. ” Edited large packet sizes back in.

“Elecrical Characteristics,” Added in typical supply current numbers for 100 BaseTX and 10 BaseTX

operation. “Register 18,” Added in note for illegal half-duplex, force flow control. “Pin Description,” Added

extra X1 clock input description. “Elecrical Characteristics,” Updated to chip only current numbers.

Added SPI Timing. Feature Highlights.

1.10

7/29/02

“Pin Description,” changed SMRXC and SMTXC to I/O. Input in MAC mode, output in PHY mode MII.

“Elecrical Characteristics,” modified current consumption to chip only numbers. “Half-Duplex Back

Pressure,” added description for no dropped packets in half-duplex mode. Added recommended

operating conditions. Added Idle mode current consumption in “Elecrical Characteristics,” added

“Selection of Isolation Transformers,” Added 3.01k

resistor instructions for ISET “Pin Description”

section. Changed Polarity of transmit pairs in “Pin Description.” Changed description for Register 2, bit 1,

in “Register Description” section. Added “Reset Timing” section.

1.11

12/17/02

“Register 3” changed 802.1x to 802.3x. “Register 6,” changed default column to disable flow control for

pull-down, and enable flow control for pull-up. “Register 29” and “Register 0” indicate loop back is at the

PHY. Added description to register 4 bit 2 to indicate that STPID packets from CPU to normal ports are

not allowed as 1522 byte tag packets. Fixed dynamic MAC address example errors in “Dynamic MAC

Address Table.” Changed definition of forced MDI, MDIX in section “Register 29,” “Register 30” and

“Register 0.” Added “Part Ordering Information.” Added Ambient operating temperature for KS8995MI

1.12

3/10/03

Changed pin 120 description to NC. Changed SPIQ pin description to Otri. Changed logo. Changed

contact information.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RSM40DTAT | CONN EDGECARD 80POS R/A .156 SLD |

| LFEC6E-3QN208C | IC FPGA 6.1KLUTS 147I/O 208-PQFP |

| LFEC6E-3Q208C | IC FPGA 6.1KLUTS 147I/O 208-PQFP |

| RMM40DTAT | CONN EDGECARD 80POS R/A .156 SLD |

| LFXP3E-5Q208C | IC FPGA 3.1KLUTS 136I/O 208-PQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KSZ8995MA | 功能描述:以太網(wǎng) IC 5 Port 10/100 Switch with PHY and Frame Buffers (Lead Free) RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| KSZ8995MA4 | 功能描述:IC SWITCH 5-PORT 10/100 128PQFP RoHS:是 類(lèi)別:集成電路 (IC) >> 專(zhuān)用 IC 系列:* 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類(lèi)型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類(lèi)型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| KSZ8995MAB3 | 功能描述:IC SWITCH 5-PORT 10/100 128PQFP RoHS:是 類(lèi)別:集成電路 (IC) >> 專(zhuān)用 IC 系列:* 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類(lèi)型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類(lèi)型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| KSZ8995MA-EVAL | 功能描述:以太網(wǎng)開(kāi)發(fā)工具 KSZ8995MA Evaluation Board RoHS:否 制造商:Micrel 產(chǎn)品:Evaluation Boards 類(lèi)型:Ethernet Transceivers 工具用于評(píng)估:KSZ8873RLL 接口類(lèi)型:RMII 工作電源電壓: |

| KSZ8995MAI | 功能描述:以太網(wǎng) IC 5 Port 10/100 Switch with PHY and Frame Buffers (Lead Free) RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。