- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄30751 > LM4550VH/NOPB (NATIONAL SEMICONDUCTOR CORP) SPECIALTY CONSUMER CIRCUIT, PQFP48 PDF資料下載

參數(shù)資料

| 型號: | LM4550VH/NOPB |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| 封裝: | 7 X 7 X 1.40 MM, LQFP-48 |

| 文件頁數(shù): | 11/30頁 |

| 文件大小: | 611K |

| 代理商: | LM4550VH/NOPB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁

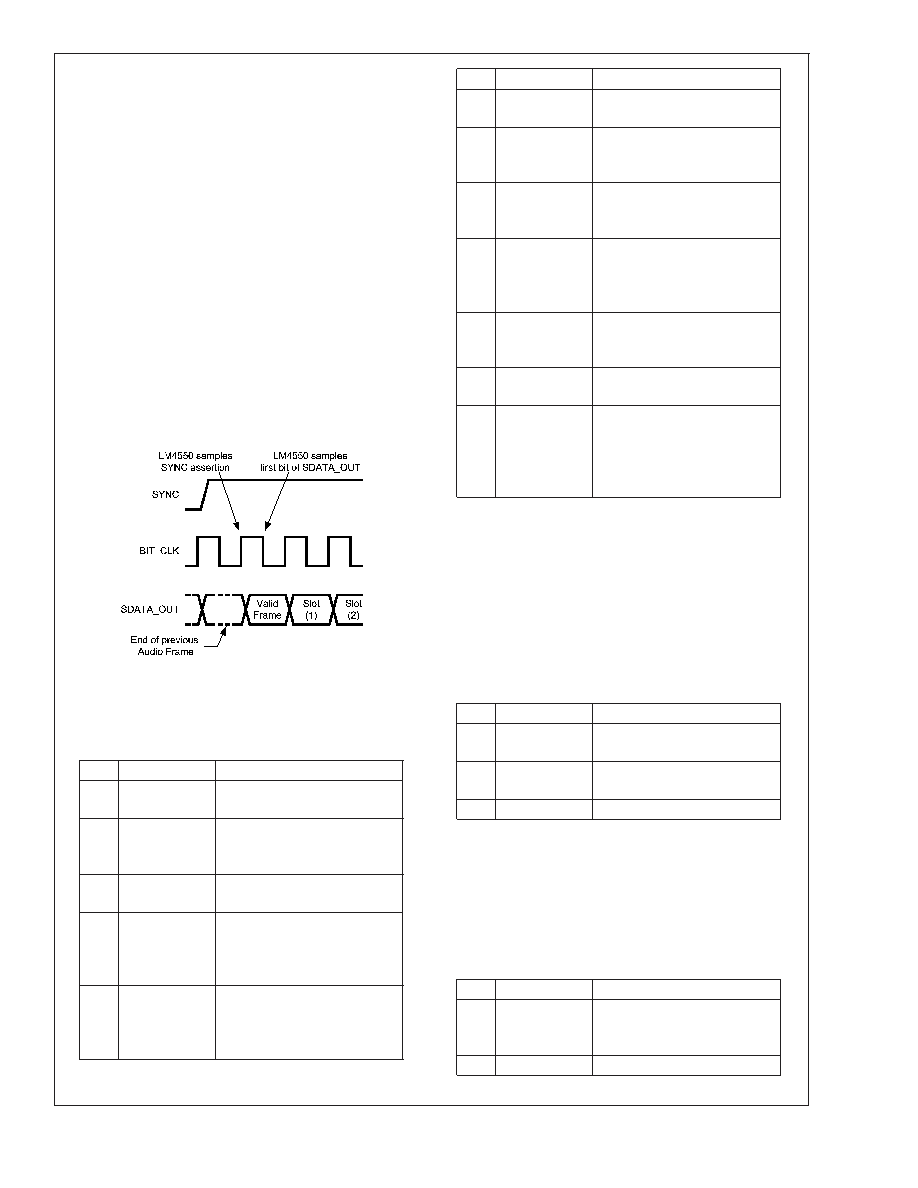

AC Link Serial Interface Protocol

(Continued)

data from four slots in a given frame and so only checks the

valid-data bits for 4 slots. In Primary mode these tag bits are

for: slot 1 (Command Address), slot 2 (Command Data), slot

3 (PCM data for left DAC) and slot 4 (PCM data for right

DAC).

The last two bits in the Tag contain the Codec ID used to

select the target codec to receive the frame in multiple codec

systems. When the frame is being sent to a codec in one of

the Secondary modes the controller does not use bits 14 and

13 to indicate valid Command Address and Data in slots 1

and 2. Instead, this role is performed by the Codec ID bits –

operation of the Extended AC Link assumes that the control-

ler would not access a secondary codec unless it was pro-

viding valid Command Address and/or Data. When in one of

the secondary modes the LM4550 only checks the tag bits

for the Codec ID and for valid data in the two audio data

slots: slots3&4for Secondary mode 1, slots7&8for mode

2 and slots6&9for mode 3.

When sending an Output Frame to a Secondary mode co-

dec, a controller should set tag bits 14 and 13 to zero.

SLOT 0, OUTPUT FRAME

Bit

Description

Comment

15

Valid Frame

1 = Valid data in at least one

slot.

14

Control register

address

1 = Valid Control Address in

Slot 1 (Primary codec

only)

13

Control register

data

1 = Valid Control Data in Slot

2 (Primary codec only)

12

Left DAC data

in Slot 3

1 = Valid PCM Data in Slot 3

(Primary & Secondary 1

modes; Left Channel

audio)

11

Right DAC data

in Slot 4

1 = Valid PCM Data in Slot 4

(Primary & Secondary 1

modes; Right Channel

audio)

Bit

Description

Comment

10

Not Used

Controller should stuff this slot

with “0”s

9

Left DAC data

in Slot 6

1 = Valid PCM Data in Slot 6

(Secondary 3 mode;

Center Channel audio)

8

Left DAC data

in Slot 7

1 = Valid PCM Data in Slot 7

(Secondary 2 mode; Left

Surround Channel audio)

7

Right DAC data

in Slot 8

1 = Valid PCM Data in Slot 8

(Secondary 2 mode;

Right Surround Channel

audio)

6

Right DAC data

in Slot 9

1 = Valid PCM Data in Slot 9

(Secondary 3 mode; LFE

Channel audio)

5:2

Not Used

Controller should stuff these

slots with “0”s

1,0

Codec ID

(ID1, ID0)

The Codec ID (Table 1) selects

the target codec in a

multi-codec system to receive

the control address and data

carried in the Output Frame

SDATA_OUT: Slot 1 – Read/Write, Control Address

Slot 1 is used by a controller to indicate both the address of

a target register in the LM4550 and whether the access

operation is a register read or register write. The MSB of slot

1 (bit 19) is set to 1 to indicate that the current access

operation is ’read’. Bits 18 through 12 are used to specify the

7-bit register address of the read or write operation. The

least significant twelve bits are reserved and should be

stuffed with zeros by the AC ’97 controller.

SLOT 1, OUTPUT FRAME

Bits

Description

Comment

19

Read/Write

1 = Read

0 = Write

18:12

Register

Address

Identifies the Status/Command

register for read/write

11:0

Reserved

Controller should set to "0"

SDATA_OUT: Slot 2 – Control Data

Slot 2 is used to transmit 16-bit control data to the LM4550

when the access operation is ’write’. The least significant

four bits should be stuffed with zeros by the AC ’97 controller.

If the access operation is a register read, the entire slot, bits

19 through 0 should be stuffed with zeros.

SLOT 2, OUTPUT FRAME

Bits

Description

Comment

19:4

Control

Register Write

Data

Controller should stuff with

zeros if operation is “read”

3:0

Reserved

Set to "0"

10097205

FIGURE 5. Start of AC Link Output Frame

LM4550

www.national.com

19

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LM4550VHX/NOPB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| LM4560VJG | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| LM4651N/NOPB | 170 W, 1 CHANNEL, AUDIO AMPLIFIER, PDIP28 |

| LM4652TF/NOPB | 170 W, 1 CHANNEL, AUDIO AMPLIFIER, PZFM15 |

| LM4663MT/NOPB | 2.1 W, 2 CHANNEL, AUDIO AMPLIFIER, PDSO24 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LM4550VHX | 制造商:Rochester Electronics LLC 功能描述:AC '97 REV 2.1 CODEC - Bulk |

| LM4550VHX/NOPB | 制造商:Texas Instruments 功能描述:Audio Codec 2ADC / 2DAC 18-Bit 48-Pin LQFP T/R |

| LM4558 | 制造商:HTC 制造商全稱:HTC Korea TAEJIN Technology Co. 功能描述:DUAL OPERATIONAL AMPLIFIERS |

| LM4558_08 | 制造商:HTC 制造商全稱:HTC Korea TAEJIN Technology Co. 功能描述:DUAL OPERATIONAL AMPLIFIERS |

| LM4558D | 制造商:HTC 制造商全稱:HTC Korea TAEJIN Technology Co. 功能描述:DUAL OPERATIONAL AMPLIFIERS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。