- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383288 > LP1072 (飛思卡爾半導(dǎo)體(中國)有限公司) 802.11a/b/g Baseband System Solution PDF資料下載

參數(shù)資料

| 型號: | LP1072 |

| 廠商: | 飛思卡爾半導(dǎo)體(中國)有限公司 |

| 英文描述: | 802.11a/b/g Baseband System Solution |

| 中文描述: | 802.11a/b/g無線基帶系統(tǒng)解決方案 |

| 文件頁數(shù): | 13/32頁 |

| 文件大?。?/td> | 293K |

| 代理商: | LP1072 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

LP1072 Interfaces

LP1072 Advance Information, Rev. 0.3

Freescale Semiconductor

13

PRELIMINARY

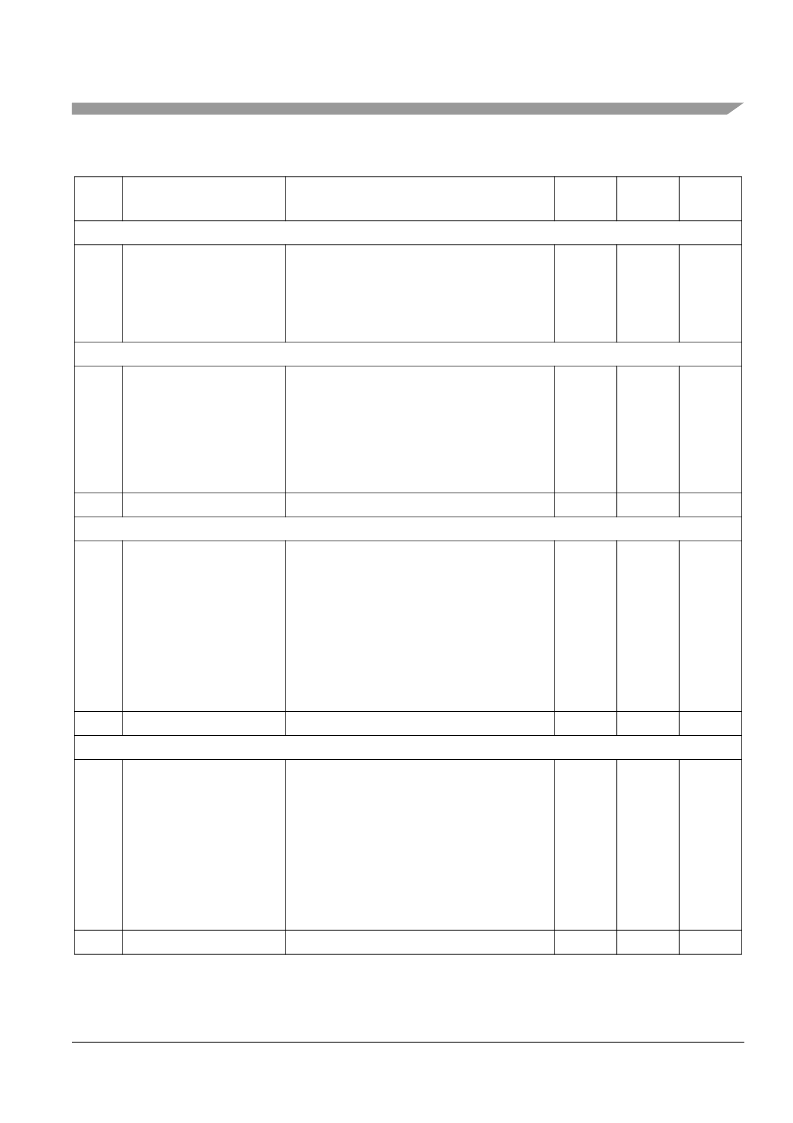

Device to SDIO Host Interrupt Enable 0 (0x0017)

7:0

Arm_to_sdio_inte_en[7:0]

Individual bit enables for each of the device to host

interrupt source bits. Setting the corresponding bit

to a “1” enables the interrupt; “0” disables the

interrupt. The SDIO Host can disable all interrupts

by disabling the main SDIO host interrupt in the

CCCR register.

-

RW

0’s

Device to SDIO Host Interrupt Enable 1 (0x0018)

2:0

Arm_to_sdio_inte_en[10:8]

Individual bit enables for each of the device to host

interrupt source bits. Setting the corresponding bit

to a “1” enables the interrupt; “0” disables the

interrupt. The SDIO Host can disable all interrupts

by disabling the main SDIO host interrupt in the

CCCR register.

Bit 0 is enable for semaphore 0 granted; bit 1 is

semaphore 1; and bit 2 is semaphore 2.

-

RW

0’s

7:3

-

Reserved

-

-

-

SDIO Host Mailbox Semaphore 0 Register (offset 0x001C)

1:0

Sdio_mbxp_0_sema

2 bit semaphore register to control whether the

host or the device has access to the shared

mailbox ram 0. The host should write a “01” to this

register to request the shared ram 0. After writing

“01” the host should read this register. If the value

is “01” then the host owns access to the mailbox.

If the value read is “11” then the device owns

access to the mailbox. When the host is done

utilizing the mailbox then it should release

ownership of the mailbox by writing “00” to this

register.

RW

RW

0’s

7:2

Reserved

-

-

-

-

SDIO Host Mailbox Semaphore 1 Register (offset 0x001D)

1:0

Sdio_mbxp_1_sema

2 bit semaphore register to control whether the

host or the device has access to the shared

mailbox ram 1. The host should write a “01” to this

register to request the shared ram 1. After writing

“01” the host should read this register. If the value

is “01” then the host owns access to the mailbox.

If the value read is “11” then the device owns

access to the mailbox. When the host is done

utilizing the mailbox then it should release

ownership of the mailbox by writing “00” to this

register.

RW

RW

0’s

7:2

Reserved

-

-

-

-

Table 8. SDIO Function 1 Registers (continued)

Bit

Name

Description

ARM

Access

HOST

Access

Reset

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LPR30 | LOW DROP VOLTAGE REGULATOR DRIVE FOR EXTERNAL N-CHANNEL POWER MOSFET |

| LPR30D | LOW DROP VOLTAGE REGULATOR DRIVE FOR EXTERNAL N-CHANNEL POWER MOSFET |

| LPR30D-TR | LOW DROP VOLTAGE REGULATOR DRIVE FOR EXTERNAL N-CHANNEL POWER MOSFET |

| LPR30N | LOW DROP VOLTAGE REGULATOR DRIVE FOR EXTERNAL N-CHANNEL POWER MOSFET |

| LRI512 | Memory TAG IC 512 bit High Endurance EEPROM 13.56MHz, ISO 15693 Standard Compliant with E.A.S. |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LP108 | 功能描述:開關(guān)配件 UNDERLOAD RoHS:否 制造商:C&K Components 類型:Cap 用于:Pushbutton Switches 設(shè)計目的: |

| LP1083 | 制造商:FCI 制造商全稱:First Components International 功能描述:LOW DROPOUT POSITVITE ADJUSTABLE REGULATOR |

| LP1083CM | 制造商:FCI 制造商全稱:First Components International 功能描述:LOW DROPOUT POSITVITE ADJUSTABLE REGULATOR |

| LP1083CZ | 制造商:FCI 制造商全稱:First Components International 功能描述:LOW DROPOUT POSITVITE ADJUSTABLE REGULATOR |

| LP1083IZ | 制造商:FCI 制造商全稱:First Components International 功能描述:LOW DROPOUT POSITVITE ADJUSTABLE REGULATOR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。