- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383288 > LP1072 (飛思卡爾半導(dǎo)體(中國)有限公司) 802.11a/b/g Baseband System Solution PDF資料下載

參數(shù)資料

| 型號: | LP1072 |

| 廠商: | 飛思卡爾半導(dǎo)體(中國)有限公司 |

| 英文描述: | 802.11a/b/g Baseband System Solution |

| 中文描述: | 802.11a/b/g無線基帶系統(tǒng)解決方案 |

| 文件頁數(shù): | 21/32頁 |

| 文件大小: | 293K |

| 代理商: | LP1072 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

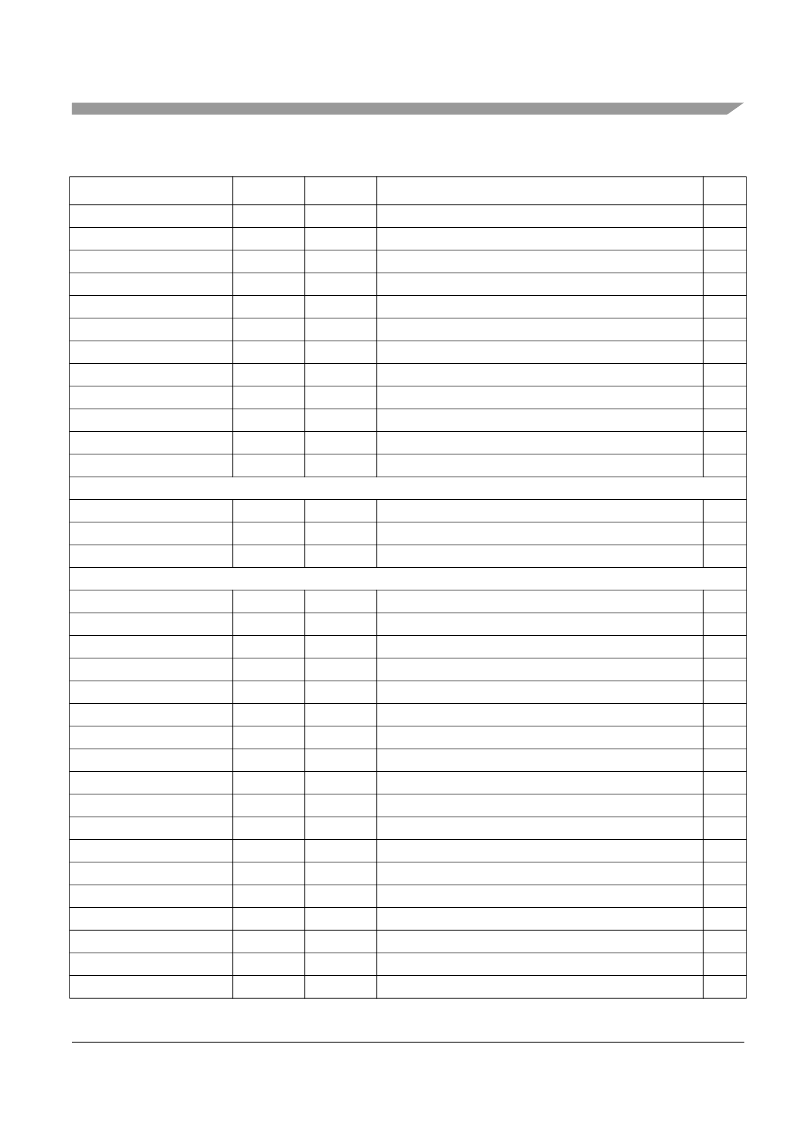

Pinout and Footprint

LP1072 Advance Information, Rev. 0.3

Freescale Semiconductor

21

PRELIMINARY

IADCINN

pdiana2p

Input

Negative input of I-ADC

A8

IADCINP

pdiana2p

Input

Positive input of I-ADC

B8

QADCINN

pdiana2p

Input

Negative input of Q-ADC

B6

QADCINP

pdiana2p

Input

Positive input of Q-ADC

C6

RSSIADCIN

pdiana2p

Input

RSSI ADC input

B1

VOCM

pdiana2p

Input

Input pin for definition of IQDAC output common -mode level

D9

AUXDACOUT

pdiana2p

Output

Auxiliary DAC output

C4

IDACOUTP

pdiana2p

Output

Positive output of I-DAC

B9

IDACOUTN

pdiana2p

Output

Negative output of I-DAC

C9

QDACOUTP

pdiana2p

Output

Positive output of Q-DAC

B10

QDACOUTN

pdiana2p

Output

Negative output of Q-DAC

A10

EXT_BIAS

pdiana2p

Input

External Bias for test

D4

TCXO Squarer

AVDD_TCXO

pvdd3p

N/A

Analog 3.3 volt

F4

AVSS_TCXO

pvss3p

N/A

Analog ground

G5

CLKIN

pdiana2p

Input

TCXO reference clock input

F1

RF Interface Signals

RF_ANALOG_LDO

pdb04dgz

Bi-dir

LDO enable for RF VCO power. Driven by PHY controller.

M9

RF_EN

pdb04dgz

Bi-dir

RF enable. Driven by PHY controller.

R12

RF_RXEN

pdb04dgz

Bi-dir

RF Rx enable. Driven by PHY controller.

P11

RF_TXEN

pdb04dgz

Bi-dir

RF Tx enable. Driven by PHY controller.

N13

RF_PAEN1

pdb04dgz

Bi-dir

RF PA enable 1. Driven by PHY controller.

P14

RF_PAEN2

pdb04dgz

Bi-dir

RF PA enable 2. Driven by PHY controller.

M13

RF_SPARE1

pdb04dgz

Bi-dir

RF spare 1 (not used). Driven by PHY controller.

L12

RF_SPARE2

pdb04dgz

Bi-dir

RF spare 2 (not used). Driven by PHY controller.

G13

RF_VGA6

pdb04dgz

Bi-dir

RF VGA setting. Driven by UWA.

M14

RF_VGA5

pdb04dgz

Bi-dir

RF VGA setting. Driven by UWA.

N15

RF_VGA4

pdb04dgz

Bi-dir

RF VGA setting. Driven by UWA.

M15

RF_VGA3

pdo02cdg

Output

RF VGA setting. Driven by UWA.

K13

RF_VGA2

pdo02cdg

Output

RF VGA setting. Driven by UWA.

L14

RF_VGA1

pdo02cdg

Output

RF VGA setting. Driven by UWA.

L15

RF_VGA0

pdo02cdg

Output

RF VGA setting. Driven by UWA.

J13

RF_RXHP

pdo02cdg

Output

RF Rx highpass filter setting. Driven by UWA.

H12

RF_ANTENNA_SEL

pdo02cdg

Output

RF antenna select. Driven by ARM.

H13

RF_ANTENNA_SEL_N

pdo02cdg

Output

RF antenna select. Driven by ARM.

J15

Table 9. Pin Description (continued)

Pad Name

Pad Type

Direction

Description

Pin

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LPR30 | LOW DROP VOLTAGE REGULATOR DRIVE FOR EXTERNAL N-CHANNEL POWER MOSFET |

| LPR30D | LOW DROP VOLTAGE REGULATOR DRIVE FOR EXTERNAL N-CHANNEL POWER MOSFET |

| LPR30D-TR | LOW DROP VOLTAGE REGULATOR DRIVE FOR EXTERNAL N-CHANNEL POWER MOSFET |

| LPR30N | LOW DROP VOLTAGE REGULATOR DRIVE FOR EXTERNAL N-CHANNEL POWER MOSFET |

| LRI512 | Memory TAG IC 512 bit High Endurance EEPROM 13.56MHz, ISO 15693 Standard Compliant with E.A.S. |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LP108 | 功能描述:開關(guān)配件 UNDERLOAD RoHS:否 制造商:C&K Components 類型:Cap 用于:Pushbutton Switches 設(shè)計(jì)目的: |

| LP1083 | 制造商:FCI 制造商全稱:First Components International 功能描述:LOW DROPOUT POSITVITE ADJUSTABLE REGULATOR |

| LP1083CM | 制造商:FCI 制造商全稱:First Components International 功能描述:LOW DROPOUT POSITVITE ADJUSTABLE REGULATOR |

| LP1083CZ | 制造商:FCI 制造商全稱:First Components International 功能描述:LOW DROPOUT POSITVITE ADJUSTABLE REGULATOR |

| LP1083IZ | 制造商:FCI 制造商全稱:First Components International 功能描述:LOW DROPOUT POSITVITE ADJUSTABLE REGULATOR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。