- 您現(xiàn)在的位置:買賣IC網 > PDF目錄16967 > MA180023 (Microchip Technology)MODULE PLUG-IN PIC18F46J11 PIM PDF資料下載

參數(shù)資料

| 型號: | MA180023 |

| 廠商: | Microchip Technology |

| 文件頁數(shù): | 185/228頁 |

| 文件大小: | 0K |

| 描述: | MODULE PLUG-IN PIC18F46J11 PIM |

| 產品培訓模塊: | PIC18 J Series MCU Overview |

| 標準包裝: | 1 |

| 系列: | PIC® |

| 附件類型: | 插拔式模塊(PIM)- PIC18F46J11 |

| 適用于相關產品: | HPC Explorer 板(DM183022)或 PIC18 Explorer 板(DM183032) |

| 產品目錄頁面: | 658 (CN2011-ZH PDF) |

| 配用: | DM183032-ND - BOARD EXPLORER PICDEM PIC18 DM183022-ND - BOARD DEMO PIC18FXX22 64/80TQFP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁當前第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁第228頁

PIC18F46J11 FAMILY

DS39932D-page 6

2011 Microchip Technology Inc.

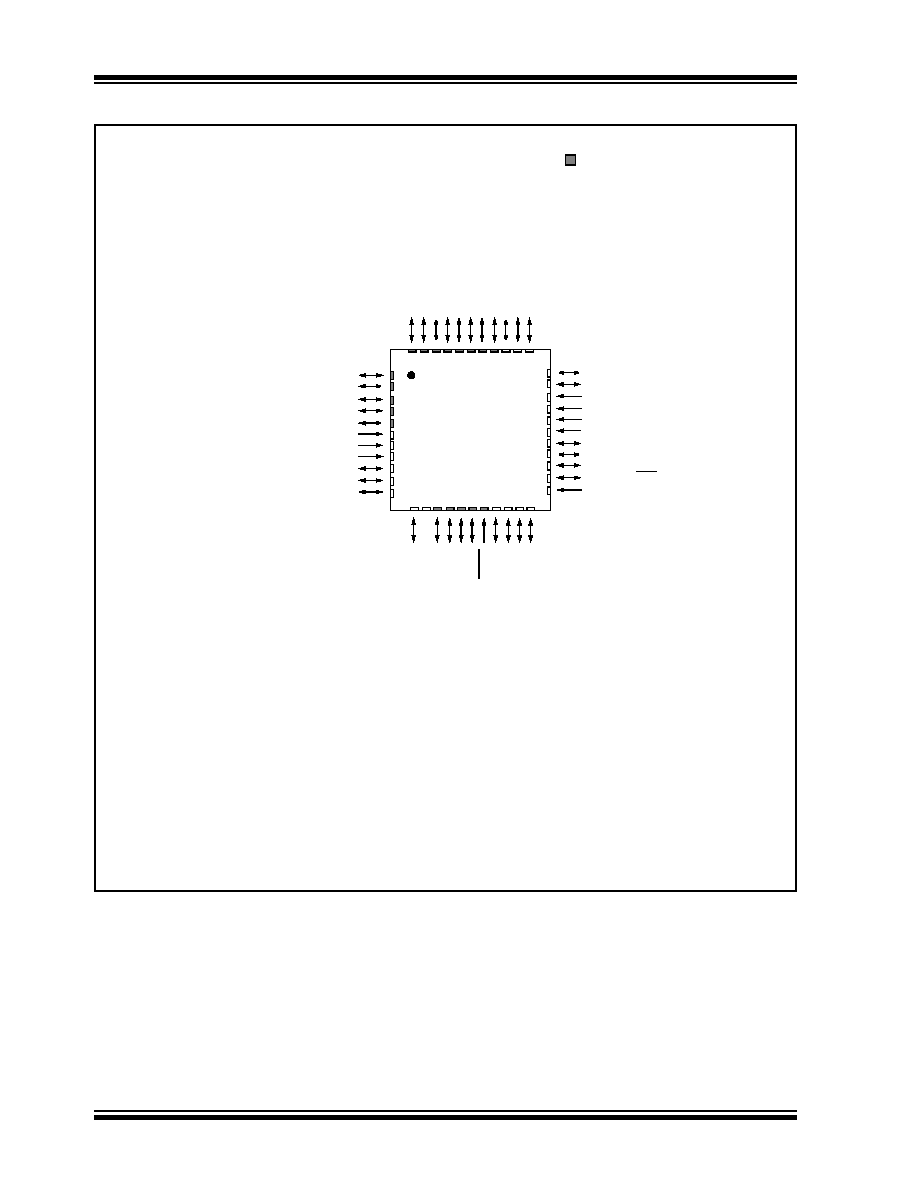

Pin Diagrams (Continued)

44-Pin QFN(1,3)

10

11

2

3

6

1

18

19

20 21 22

12 13

14 15

38

8

7

44

43

42 41

40 39

16 17

29

30

31

32

33

23

24

25

26

27

28

36

34

35

9

PIC18F4XJ11

37

RA3

/A

N

3

/V

RE

F

+/C1

INB

R

A

2/

A

N

2/V

RE

F-/

C

V

RE

F

-/C

2

IN

B

RA1

/AN1

/C2

IN

A/

P

M

A7

/RP1

RA

0

/AN0

/C

1I

N

A/

UL

P

W

U/

PM

A6

/RP0

MC

L

R

B

7/K

B

I3/

P

G

D

/RP1

0

R

B

6

/KBI

2/

PG

C/

RP9

RB5

/PM

A

0

/KBI

1/

RP

8

RB4

/P

M

A1

/KBI

0

/RP7

NC

R

C

6/

P

M

A5

/T

X1

/C

K

1/

RP1

7

RC

5/

S

D

O

1

/RP1

6

R

C

4/S

D

I1

/S

DA

1\

RP1

5

RD

3/

P

M

D

3/

RP2

0

RD

2/

P

M

D

2/

RP1

9

R

D

1/

PM

D1

/SDA2

R

D

0/

PM

D0

/SCL

2

R

C

3\

SCK1

/S

CL

1/

RP1

4

RC

2/

A

N

11

/C

T

P

L

S

/RP

1

3

R

C

1/T

1OS

I/

RP1

2

RC0/T

1O

S

O

/T

1CK

I/

RP1

1

OSC2/CLKO/RA6

OSC1/CLKI/RA7

VSS

AVDD

RE2/AN7/PMCS

RE1/AN6/PMWR

RE0/AN5/PMRD

RA5/AN4/SS1/HLVDIN/RP2

VDDCORE/VCAP(2)

RC7/PMA4/RX1/DT1/RP18

RD4/PMD4/RP21

RD5/PMD5/RP22

RD6/PMD6/RP23

VSS

VDD

RB0/AN12/INT0/RP3

RB1/AN10/PMBE/RTCC/RP4

RB2/AN8/CTED1/PMA3/REFO/RP5

RB

3

/AN9

/CTED2

/P

M

A2

/RP6

RD7/PMD7/RP24

5

4

AVSS

VDD

AVDD

Legend:

RPn

represents remappable pins.

Note

1:

Some input and output functions are routed through the Peripheral Pin Select (PPS) module and can be

dynamically assigned to any of the RPn pins. For a list of the input and output functions, see Table 10-13

and Table 10-14, respectively. For details on configuring the PPS module, see Section 10.7 “Peripheral

.

2:

3:

For the QFN package, it is recommended that the bottom pad be connected to VSS.

= Pins are up to 5.5V tolerant

相關PDF資料 |

PDF描述 |

|---|---|

| 1-1589476-8 | CONN RCPT 15POS 32AWG 24IN |

| 0210490389 | CABLE JUMPER 1.25MM .051M 32POS |

| 0982660969 | CBL 27POS 0.5MM JMPR TYPE A 3" |

| 1-1589457-4 | CONN RCPT 15POS 30AWG 24IN |

| 0982660968 | CBL 27POS 0.5MM JMPR TYPE D 3" |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MA180024 | 功能描述:子卡和OEM板 PIC18F46J50 FS USB PIM DEMO BOARD RoHS:否 制造商:BeagleBoard by CircuitCo 產品:BeagleBone LCD4 Boards 用于:BeagleBone - BB-Bone - Open Source Development Kit |

| MA180025 | 功能描述:子卡和OEM板 PIM for PIC18F87J90 w/ Cap Touch buttons RoHS:否 制造商:BeagleBoard by CircuitCo 產品:BeagleBone LCD4 Boards 用于:BeagleBone - BB-Bone - Open Source Development Kit |

| MA180026 | 功能描述:子卡和OEM板 PIC18F45K20 44P TQFP to 84P PIM RoHS:否 制造商:BeagleBoard by CircuitCo 產品:BeagleBone LCD4 Boards 用于:BeagleBone - BB-Bone - Open Source Development Kit |

| MA180027 | 功能描述:子卡和OEM板 PIC18F87K90 PIM w/ Cap Touch RoHS:否 制造商:BeagleBoard by CircuitCo 產品:BeagleBone LCD4 Boards 用于:BeagleBone - BB-Bone - Open Source Development Kit |

| MA180028 | 功能描述:子卡和OEM板 PIC18F87K22 Plug-In Module RoHS:否 制造商:BeagleBoard by CircuitCo 產品:BeagleBone LCD4 Boards 用于:BeagleBone - BB-Bone - Open Source Development Kit |

發(fā)布緊急采購,3分鐘左右您將得到回復。