- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16967 > MA180023 (Microchip Technology)MODULE PLUG-IN PIC18F46J11 PIM PDF資料下載

參數(shù)資料

| 型號: | MA180023 |

| 廠商: | Microchip Technology |

| 文件頁數(shù): | 43/228頁 |

| 文件大小: | 0K |

| 描述: | MODULE PLUG-IN PIC18F46J11 PIM |

| 產(chǎn)品培訓(xùn)模塊: | PIC18 J Series MCU Overview |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | PIC® |

| 附件類型: | 插拔式模塊(PIM)- PIC18F46J11 |

| 適用于相關(guān)產(chǎn)品: | HPC Explorer 板(DM183022)或 PIC18 Explorer 板(DM183032) |

| 產(chǎn)品目錄頁面: | 658 (CN2011-ZH PDF) |

| 配用: | DM183032-ND - BOARD EXPLORER PICDEM PIC18 DM183022-ND - BOARD DEMO PIC18FXX22 64/80TQFP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁當(dāng)前第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁第228頁

2010 Microchip Technology Inc.

DS70138G-page 137

dsPIC30F3014/4013

19.9

Module Power-Down Modes

The module has two internal power modes.

When the ADON bit is ‘1’, the module is in Active mode;

it is fully powered and functional.

When ADON is ‘0’, the module is in Off mode. The

digital and analog portions of the circuit are disabled for

maximum current savings.

In order to return to the Active mode from Off mode, the

user must wait for the ADC circuitry to stabilize. The

time required to stabilize is specified in Section 23.0

19.10 A/D Operation During CPU Sleep

and Idle Modes

19.10.1

A/D OPERATION DURING CPU

SLEEP MODE

When the device enters Sleep mode, all clock sources

to the module are shut down and stay at logic ‘0’.

If Sleep occurs in the middle of a conversion, the

conversion is aborted. The converter does not continue

with a partially completed conversion on exit from

Sleep mode.

Register contents are not affected by the device

entering or leaving Sleep mode.

The A/D module can operate during Sleep mode if the

A/D clock source is set to RC (ADRC = 1). When the

RC clock source is selected, the A/D module waits one

instruction cycle before starting the conversion. This

allows the SLEEP instruction to be executed which

eliminates all digital switching noise from the conver-

sion. (When the conversion sequence is complete, the

DONE bit is set.)

If the A/D interrupt is enabled, the device wakes up

from Sleep. If the A/D interrupt is not enabled, the A/D

module is then turned off, although the ADON bit

remains set.

19.10.2

A/D OPERATION DURING CPU IDLE

MODE

The ADSIDL bit determines if the module stops or

continues on Idle. If ADSIDL = 0, the module continues

operation on assertion of Idle mode. If ADSIDL = 1, the

module stops on Idle.

19.11 Effects of a Reset

A device Reset forces all registers to their Reset state.

This forces the A/D module to be turned off, and any

conversion and sampling sequence is aborted. The val-

ues that are in the ADCBUF registers are not modified.

The A/D Result register contains unknown data after a

Power-on Reset.

19.12 Output Formats

The A/D result is 12 bits wide. The data buffer RAM is

also 12 bits wide. The 12-bit data can be read in one

of four different formats. The FORM<1:0> bits select

the format. Each of the output formats translates to a

16-bit result on the data bus. Write data is always in

right-justified (integer) format.

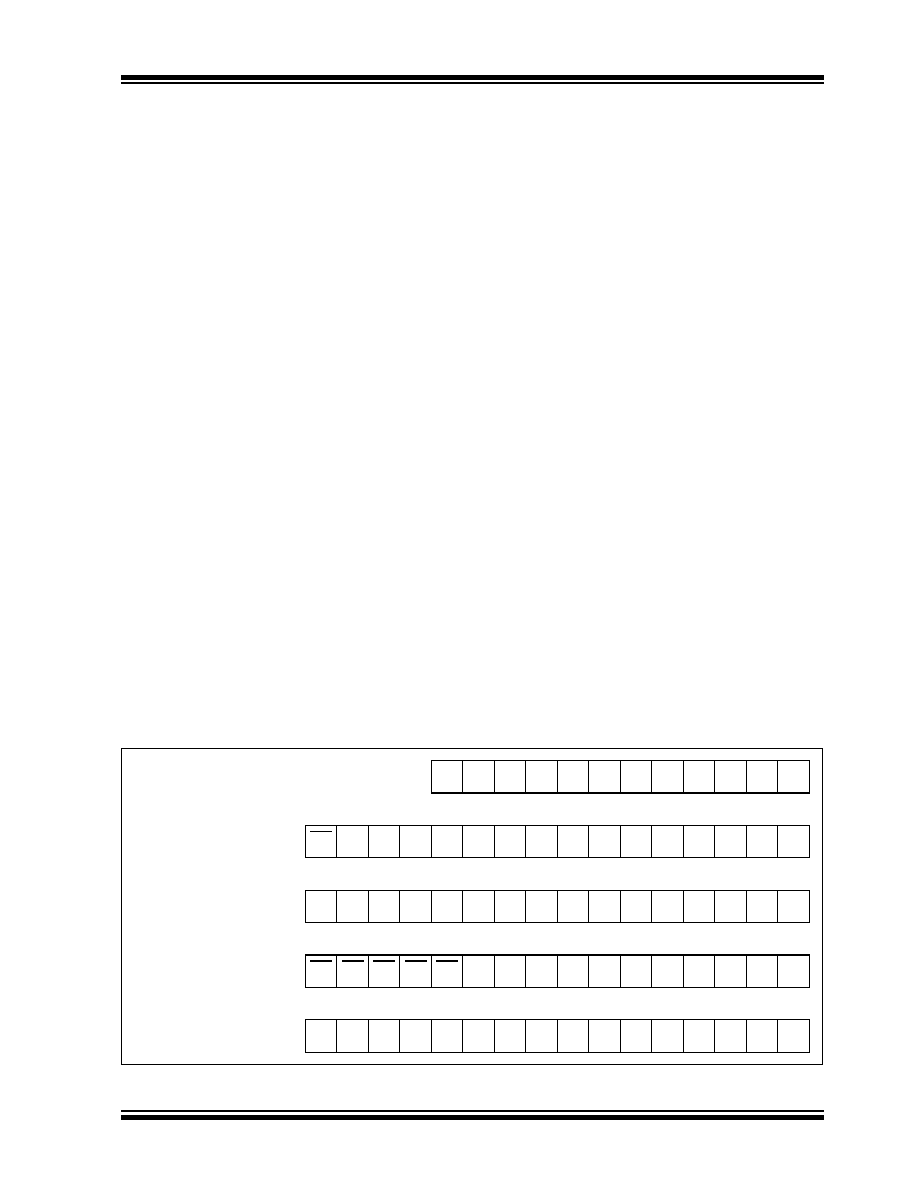

FIGURE 19-5:

A/D OUTPUT DATA FORMATS

RAM Contents:

d11 d10 d09 d08 d07 d06 d05 d04 d03 d02 d01 d00

Read to Bus:

Signed Fractional

d11 d10 d09 d08 d07 d06 d05 d04 d03 d02 d01 d00

0000

Fractional

d11 d10 d09 d08 d07 d06 d05 d04 d03 d02 d01 d00

0000

Signed Integer

d11 d11 d11 d11 d11 d10 d09 d08 d07 d06 d05 d04 d03 d02 d01 d00

Integer

0000

d11 d10 d09 d08 d07 d06 d05 d04 d03 d02 d01 d00

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 1-1589476-8 | CONN RCPT 15POS 32AWG 24IN |

| 0210490389 | CABLE JUMPER 1.25MM .051M 32POS |

| 0982660969 | CBL 27POS 0.5MM JMPR TYPE A 3" |

| 1-1589457-4 | CONN RCPT 15POS 30AWG 24IN |

| 0982660968 | CBL 27POS 0.5MM JMPR TYPE D 3" |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MA180024 | 功能描述:子卡和OEM板 PIC18F46J50 FS USB PIM DEMO BOARD RoHS:否 制造商:BeagleBoard by CircuitCo 產(chǎn)品:BeagleBone LCD4 Boards 用于:BeagleBone - BB-Bone - Open Source Development Kit |

| MA180025 | 功能描述:子卡和OEM板 PIM for PIC18F87J90 w/ Cap Touch buttons RoHS:否 制造商:BeagleBoard by CircuitCo 產(chǎn)品:BeagleBone LCD4 Boards 用于:BeagleBone - BB-Bone - Open Source Development Kit |

| MA180026 | 功能描述:子卡和OEM板 PIC18F45K20 44P TQFP to 84P PIM RoHS:否 制造商:BeagleBoard by CircuitCo 產(chǎn)品:BeagleBone LCD4 Boards 用于:BeagleBone - BB-Bone - Open Source Development Kit |

| MA180027 | 功能描述:子卡和OEM板 PIC18F87K90 PIM w/ Cap Touch RoHS:否 制造商:BeagleBoard by CircuitCo 產(chǎn)品:BeagleBone LCD4 Boards 用于:BeagleBone - BB-Bone - Open Source Development Kit |

| MA180028 | 功能描述:子卡和OEM板 PIC18F87K22 Plug-In Module RoHS:否 制造商:BeagleBoard by CircuitCo 產(chǎn)品:BeagleBone LCD4 Boards 用于:BeagleBone - BB-Bone - Open Source Development Kit |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。