- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377895 > MB86960 (Fujitsu Limited) NETWORK INTERFACE CONTROLLER with ENCODER/DECODER (NICE) PDF資料下載

參數(shù)資料

| 型號(hào): | MB86960 |

| 廠商: | Fujitsu Limited |

| 英文描述: | NETWORK INTERFACE CONTROLLER with ENCODER/DECODER (NICE) |

| 中文描述: | 網(wǎng)絡(luò)接口控制器的編碼/解碼器(尼斯) |

| 文件頁數(shù): | 23/65頁 |

| 文件大小: | 488K |

| 代理商: | MB86960 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當(dāng)前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁

MB86960

Type Descriptions (TYPE)

The following legend of descriptions applies to the type

column of the register bit description tables:

R: Readable bit

W: Writeable bit

C: Clears associated status bit and/or interrupt when 1 is

written; no effect when 0 is written

N: Not used; reserved; write only 0 when written

0/1:Initial state after hardware reset

DATA LINK CONTROL REGISTERS

Status and control bits for the transmitter and receiver

sections of the NICE chip are located in the first eight data

link control registers, DLCR0–7. See Tables 4–11 for

details.

Transmit Status Register

This register provides transmit status for the host

processor. The system can enable interrupts based on the

assertion (going high) of bits 7, 2, and/or 1 of this register

by setting the corresponding enable bits in the Transmit

Interrupt Enable register. See Table 4.

Bits 7, 2 and 1 in this register, the bits that can generate

interrupts, are cleared by writing 1 to the bit. Writing 0 to

the bit has no effect, only the NICE chip control logic can

set these bits. Clearing the bit that caused the interrupt will

clear both the bit itself and the interrupt. Since two or

more status conditions can occur at one time, the interrupt

routine must read all of them and act on all of those that are

set.

One method for clearing interrupts is to read the contents

of the status register, then write the same value back to the

register, thus clearing all bits which were set. Another

technique is to clear each status bit separately by writing

its mask to the register. This might be done as the

corresponding interrupt service is performed.

Note:

Wholesale clearing of all status bits by writing FFH to the

register is not recommended, since this may clear status

which has just been set and not yet read by the system. The

transmitter must be idle and TX DONE, DLCR0<7>,

must be cleared by writing 1 to it before starting the

transmitter (by writing 1 to TX START, BMPR10<7>).

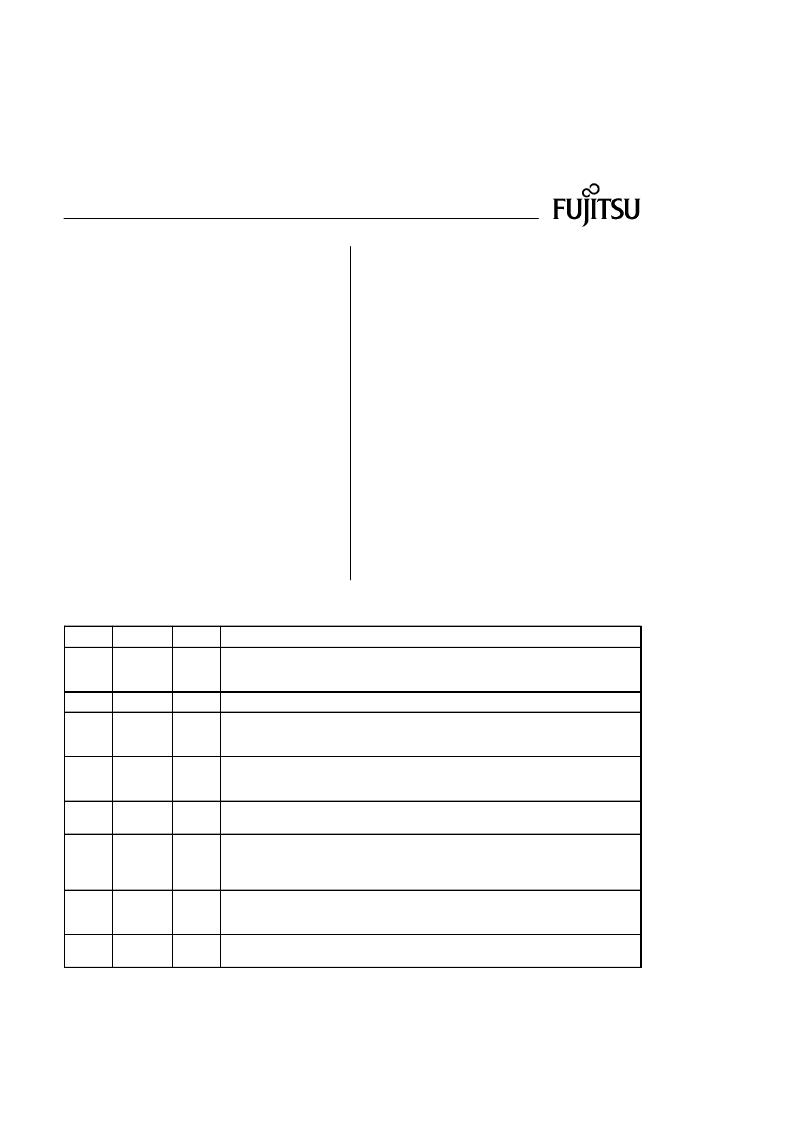

Table 4. DLCR0 — Transmit Status Register

BIT

SYMBOL

TYPE

DESCRIPTION

7

TX DONE

R

C

0

TRANSMIT DONE:

This bit is set high when all packets in the active transmit buffer have

been successfully transmitted to the LAN media, or skipped due to excessive collisions. Can

generate interrupt if enabled by DLCR2<7>.

6

NET BSY

R

NET BUSY:

This is a real-time image of the Carrier Sense signal of the receiver.

5

TX-RX

R

0

TRANSMIT PACKET RECEIVED:

Indicates that a good packet was received by NICE

shortly after transmission was completed. This is used to indicate self-reception of the

packet. This bit is cleared as each transmission begins.

4

CR LOST

R

0

CARRIER LOST:

This bit is set if the receive carrier sense input is negated during a packet

transmission. This can be caused by a collision or a shorted LAN medium. It is automatically

cleared as each transmission begins.

3

0

N

0

RESERVED:

Write 0.

2

COL

R

C

0

COLLISION:

This bit will assert during transmission of a data packet if a collision occurs on

the network. The buffer controller will automatically retransmit the current packet after

collisions up to 15 times. The user may read the number of consecutive collisions in the

collision counter, DLCR4<7:4>. Can generate interrupt if enabled by DLCR2<2>.

1

16 COL

R

C

0

16 COLLISIONS:

This bit is set after the sixteenth unsuccessful transmission of the same

packet. Can generate interrupt if enabled by DLCR2<1>.

0

0

R

O

RESERVED:

Write 0.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB86960APF-G | NETWORK INTERFACE CONTROLLER with ENCODER/DECODER (NICE) |

| MB86961A | UNIVERSAL INTERFACE FOR 10BASET |

| MB86961APD-G | UNIVERSAL INTERFACE FOR 10BASET |

| MB86961APF-G | UNIVERSAL INTERFACE FOR 10BASET |

| MB86965 | EtherCoupler ETHERNET CONTROLLER WITH 10BASE?T TRANSCEIVER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB86960APF-G | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:NETWORK INTERFACE CONTROLLER with ENCODER/DECODER (NICE) |

| MB86961A | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:UNIVERSAL INTERFACE FOR 10BASET |

| MB86961APD-G | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:UNIVERSAL INTERFACE FOR 10BASET |

| MB86961APF-G | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:UNIVERSAL INTERFACE FOR 10BASET |

| MB86965 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:EtherCoupler ETHERNET CONTROLLER WITH 10BASE?T TRANSCEIVER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。