- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄377895 > MB86960 (Fujitsu Limited) NETWORK INTERFACE CONTROLLER with ENCODER/DECODER (NICE) PDF資料下載

參數(shù)資料

| 型號(hào): | MB86960 |

| 廠(chǎng)商: | Fujitsu Limited |

| 英文描述: | NETWORK INTERFACE CONTROLLER with ENCODER/DECODER (NICE) |

| 中文描述: | 網(wǎng)絡(luò)接口控制器的編碼/解碼器(尼斯) |

| 文件頁(yè)數(shù): | 40/65頁(yè) |

| 文件大?。?/td> | 488K |

| 代理商: | MB86960 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)當(dāng)前第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)

MB86960

RECEIVER CIRCUITS

The receiver includes a receive state machine, serial to

parallel conversion, pipe-line FIFO, preamble recogni-

tion, bit and byte framing, address filtering, CRC

and other error checking and ‘end-of-packet’ symbol

recognition.

The receiver state machine provides sequencing of events

for the receiver, including idle, busy, address filtering,

data storage, etc. It detects various receive error

conditions and sets appropriate bits within the DLC

Registers.

A small data FIFO provides elastic buffering for

synchronization with the buffer controller timing, and

buffering data while the buffer controller is servicing

other buffer memory access requests.

All received bytes are delayed by four bytes before

storing in the receive buffer so that the last four bytes

of the packet can be stripped and checked for correct

CRC. (The CRC bytes are not transferred to the

receive buffer.)

During reception, packets are automatically rejected if

space in the receive buffer is insufficient to hold the entire

received packet. Status bits in the receive status register

are set to indicate this and other errors. The receive errors

are: 1) bus read error, which occurs if the host system

attempts to read from an empty receive buffer (this need

never occur if the RX BUF EMPTY bit is checked), 2)

short packet error, 3) alignment error (incomplete byte

fragment at end of packet), 4) CRC error and 5) buffer

overflow. There is one additional possible receive error

which the chip leaves to the software to check -- length

error. When the length of the packet does not match the

value in the Length Field of an 8802–3 packet, this is a

length error. Some protocols use the length field for other

purposes, for example, the DIX protocol uses it for a

packet type code. In this case, allowed type codes do not

overlap allowed packet length values, providing a means

to distinguish which protocol is being used (if length

value >1500, it’s DIX type code). Length check can be

made conditional on protocol type if necessary to support

other protocols like DIX.

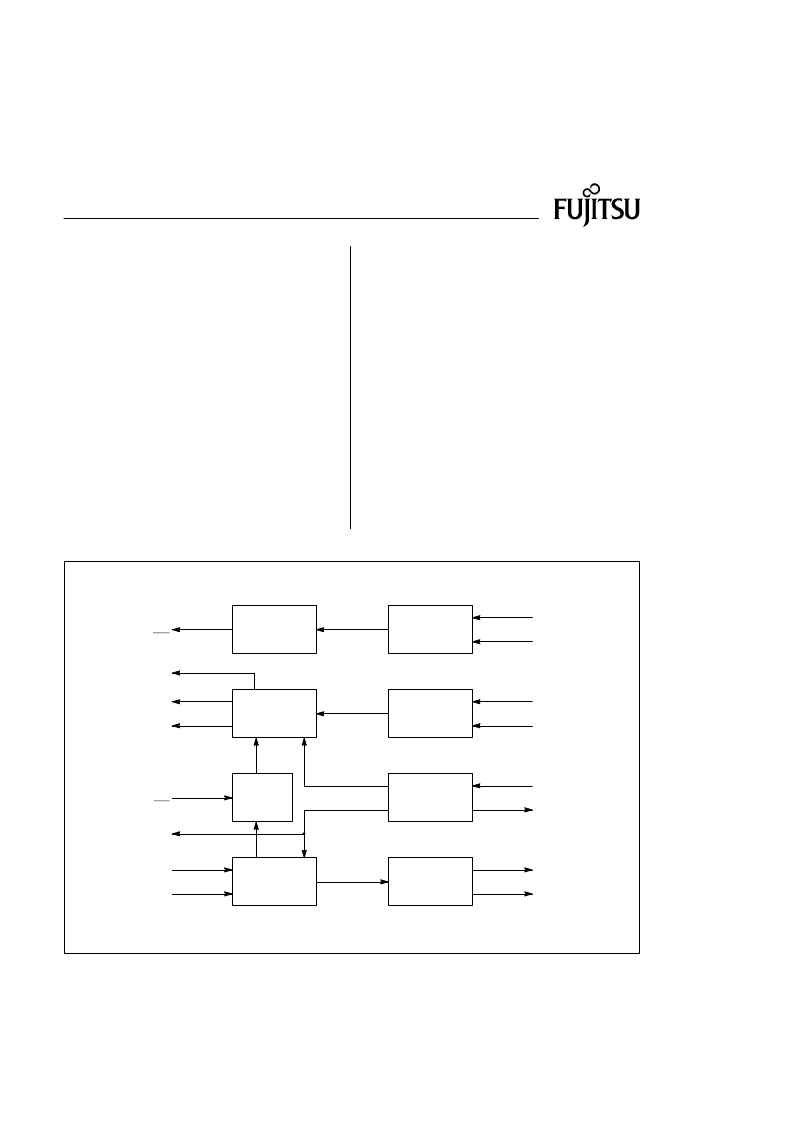

Figure 14. Encoder/Decoder Block Diagram

COLLISION

SIGNAL

DECODER

COLLISION

SIGNAL

RECEIVER

COL

INTERFACE TO

ENCODER/DECODER

AUI

INTERFACE

COL+

RXDATA+

RXDATA+

PLL

DECODER

RX LINE

RECEIVER

COL

RCK

RXD

LOOKBACK

CRYSTAL

OSCILLATOR

X2

X1

MANCHESTER

ENCODER

TX LINE

DRIVER

TXDATA

TXDATA+

TEN

TXD

LBC

TCK

CRS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB86960APF-G | NETWORK INTERFACE CONTROLLER with ENCODER/DECODER (NICE) |

| MB86961A | UNIVERSAL INTERFACE FOR 10BASET |

| MB86961APD-G | UNIVERSAL INTERFACE FOR 10BASET |

| MB86961APF-G | UNIVERSAL INTERFACE FOR 10BASET |

| MB86965 | EtherCoupler ETHERNET CONTROLLER WITH 10BASE?T TRANSCEIVER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB86960APF-G | 制造商:FUJITSU 制造商全稱(chēng):Fujitsu Component Limited. 功能描述:NETWORK INTERFACE CONTROLLER with ENCODER/DECODER (NICE) |

| MB86961A | 制造商:FUJITSU 制造商全稱(chēng):Fujitsu Component Limited. 功能描述:UNIVERSAL INTERFACE FOR 10BASET |

| MB86961APD-G | 制造商:FUJITSU 制造商全稱(chēng):Fujitsu Component Limited. 功能描述:UNIVERSAL INTERFACE FOR 10BASET |

| MB86961APF-G | 制造商:FUJITSU 制造商全稱(chēng):Fujitsu Component Limited. 功能描述:UNIVERSAL INTERFACE FOR 10BASET |

| MB86965 | 制造商:FUJITSU 制造商全稱(chēng):Fujitsu Component Limited. 功能描述:EtherCoupler ETHERNET CONTROLLER WITH 10BASE?T TRANSCEIVER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。