- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄371086 > MCM62Y308J17 (MOTOROLA INC) Synchronous Line Buffer:8K x 8 Bit Fast Static Dual Ported Memory PDF資料下載

參數(shù)資料

| 型號(hào): | MCM62Y308J17 |

| 廠商: | MOTOROLA INC |

| 元件分類(lèi): | DRAM |

| 英文描述: | Synchronous Line Buffer:8K x 8 Bit Fast Static Dual Ported Memory |

| 中文描述: | 8K X 8 MULTI-PORT SRAM, 17 ns, PDSO32 |

| 封裝: | 0.300 INCH, SOJ-32 |

| 文件頁(yè)數(shù): | 10/16頁(yè) |

| 文件大小: | 257K |

| 代理商: | MCM62Y308J17 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)

MCM62Y308

10

MOTOROLA FAST SRAM

be sampled regardless of G). Only one action will be per-

formed in the Run–Test/Idle state no matter how many clock

cycles are input. Note that TCK, not the Clock pin(K), is used

as the clock input while K is ignored during INTEST. After one

or more clock cycles of TCK, the TAP controller would then be

moved to the Shift–DR state where the sampled values would

be shifted out of TDO (and new values would be shifted in

TDI). These values would normally be compared to expected

values to test for device functionality.

THE INTEST TAP INSTRUCTION

The INTEST instruction is intended to be used to assist in

testing internal device functionality. When the INTEST instruc-

tion is loaded the boundary–scan register is placed between

TDI and TDO in the Shift–DR state of the TAP controller (Table

2). While in the Shift–DR state, all input pins would be pre-

loaded via the boundary scan register to set up the desired

mode (i.e., read, write, reload, etc.). The TAP controller would

then be moved to the Run–Test/Idle state. In this state one or

more cycles of TCK would cause the preloaded data in the

boundary–scan register to be driven while the values of

Q0 – Q7 would be sampled (Q0 – Q7 will be active only if G

is preloaded with a zero, however the values of Q0 – Q7 will

be sampled regardless of G). Only one action will be per-

formed in the Run–Test/Idle state no matter how many clock

cycles are input. Note that TCK, not the Clock pin(K), is used

as the clock input while K is ignored during INTEST. After one

or more clock cycles of TCK, the TAP controller would then be

moved to the Shift–DR state where the sampled values would

be shifted out of TDO (and new values would be shifted in

TDI). These values would normally be compared to expected

values to test for device functionality.

Since device functionality can only be verified through sam-

pling the outputs of the device, the most likely use of INTEST

would be to first load up the boundary–scan register for a Write

Reload and execute the reload in the Run–Test/Idle state.

Then a write of the first address would be performed again

using the boundary scan register to load up the input registers

and executing the write in the Run–Test/Idle state. Lastly, a

Read Reload would be executed in the same manner so that

the data that had just been written in the first address would

be read from the memory array and written into the output reg-

isters which would then be shifted out of TDO in the Shift–DR

state. The values of the roll–over flags (RRF and WRF) would

also be sampled and shifted out at the same time for compari-

son to expected values.

There are easier ways to serially read and write the memory

array. See the EZREAD and EZWRITE TAP instruction ex-

planation.

CLAMP TAP INSTRUCTION

The CLAMP instruction is provided to allow the state of the

signals driven from the output pins to be determined from the

boundary–scan register while the bypass register is selected

as the serial path between TDI and TDO. The signals driven

from the output pins will not change while the CLAMP instruc-

tion is selected. EXTEST could also be used for this purpose

but CLAMP shortens the board scan path by inserting only the

bypass register between TDI and TDO. To use CLAMP, the

SAMPLE/PRELOAD instruction would be used first to scan in

the values to be driven on the output pins when the CLAMP

instruction is active. Q0 – Q7 will be active only if G is pre-

loaded with a zero.

HIGH–Z TAP INSTRUCTION

The High–Z instruction is provided to allow all the outputs

(except TDO) to be placed in an inactive drive state (High–Z),

including the Read Roll–Over Flag and the Write Roll–Over

Flag outputs. During the High–Z instruction the bypass regis-

ter is connected between TDI and TDO.

BYPASS TAP INSTRUCTION

The Bypass instruction is the default instruction loaded in at

power up. This instruction will place a single shift register be-

tween TDI and TDO during the Shift–DR state of the TAP con-

troller. This allows the board level scan path to be shortened

to facilitate testing of other devices in the scan path.

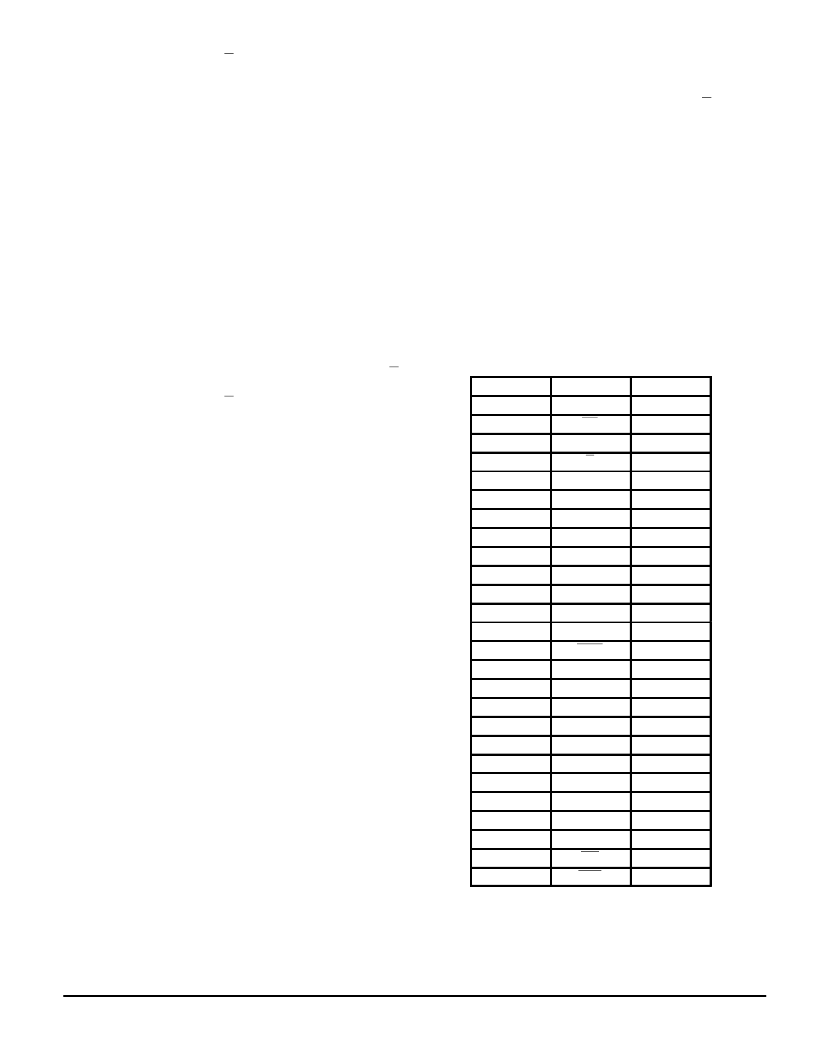

Table 2. Boundary Scan Register Bit Definitions

Bit Number

Pin Name

Pin Type

0

RRF

Output

1

RR

Input

2

RE

Input

3

G

Input

4

Q0

Output

5

Q1

Output

6

Q2

Output

7

Q3

Output

8

Q4

Output

9

Q5

Output

10

Q6

Output

11

Q7

Output

12

WRF

Output

13

WRR

Input

14

D7

Input

15

D6

Input

16

D5

Input

17

D4

Input

18

D3

Input

19

D2

Input

20

D1

Input

21

D0

Input

22

K

Input

23

WE

Input

24

WR

Input

25

RRR

Input

NOTE: K is a sample–only scan bit. It cannot be

pre–loaded for control purposes.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MCM6323A | 64K x 16 Bit 3.3 V Asynchronous Fast Static RAM |

| MCM6323AYJ10 | 64K x 16 Bit 3.3 V Asynchronous Fast Static RAM |

| MCM6323AYJ10R | 64K x 16 Bit 3.3 V Asynchronous Fast Static RAM |

| MCM6323AYJ12 | 64K x 16 Bit 3.3 V Asynchronous Fast Static RAM |

| MCM6323AYJ12R | 64K x 16 Bit 3.3 V Asynchronous Fast Static RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCM6323A | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:64K x 16 Bit 3.3 V Asynchronous Fast Static RAM |

| MCM6323ATS10 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:64K x 16 Bit 3.3 V Asynchronous Fast Static RAM |

| MCM6323ATS10R | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:64K x 16 Bit 3.3 V Asynchronous Fast Static RAM |

| MCM6323ATS12 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:64K x 16 Bit 3.3 V Asynchronous Fast Static RAM |

| MCM6323ATS12R | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:64K x 16 Bit 3.3 V Asynchronous Fast Static RAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。