- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69040 > MSP430C336IPJM (TEXAS INSTRUMENTS INC) 16-BIT, MROM, 3.8 MHz, RISC MICROCONTROLLER, PQFP100 PDF資料下載

參數(shù)資料

| 型號: | MSP430C336IPJM |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 16-BIT, MROM, 3.8 MHz, RISC MICROCONTROLLER, PQFP100 |

| 封裝: | PLASTIC, MS-022, QFP-100 |

| 文件頁數(shù): | 38/42頁 |

| 文件大?。?/td> | 637K |

| 代理商: | MSP430C336IPJM |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁當(dāng)前第38頁第39頁第40頁第41頁第42頁

MSP430C33x, MSP430P337A

MIXED SIGNAL MICROCONTROLLERS

SLAS227A – OCTOBER 1999 – REVISED JUNE 2000

5

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

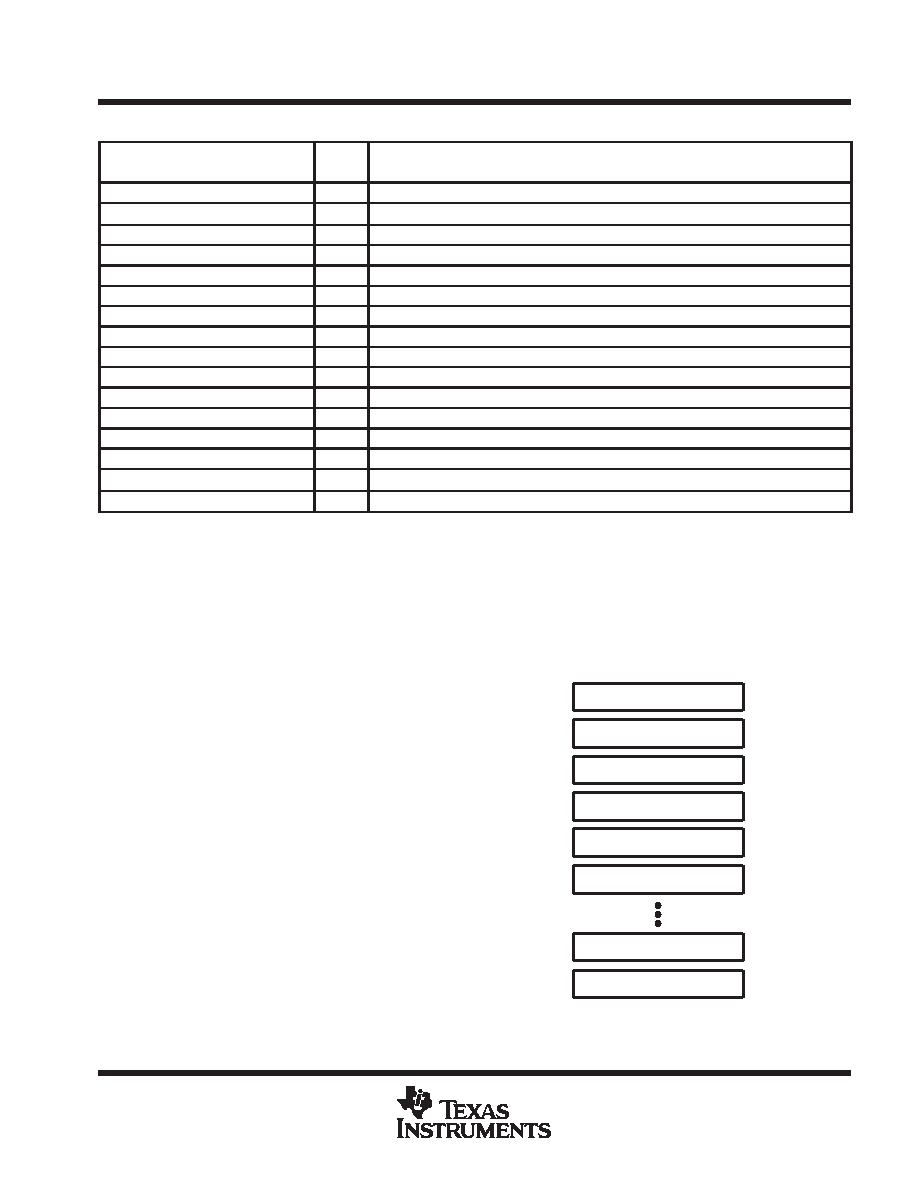

Terminal Functions (Continued)

TERMINAL

I/O

DESCRIPTION

NAME

NO.

I/O

DESCRIPTION

TMS

94

I

Test mode select. TMS is used as an input port for device programming and test.

TDO/TDI

92

I/O

Test data output port. TDO/TDI data output or programming data input terminal

TP0.0

3

O

General-purpose 3-state digital output port, bit 0 – Timer/Port

TP0.1

4

O

General-purpose 3-state digital output port, bit 1 – Timer/Port

TP0.2

5

O

General-purpose 3-state digital output port, bit 2 – Timer/Port

TP0.3

6

O

General-purpose 3-state digital output port, bit 3 – Timer/Port

TP0.4

7

O

General-purpose 3-state digital output port, bit 4 – Timer/Port

TP0.5

8

I/O

General-purpose 3-state digital input/output port, bit 5 – Timer/Port

VCC1

1

Positive supply voltage

VCC2

29

Positive supply voltage

VSS1

100

Ground reference

VSS2

28

Ground reference

VSS3

52

Ground reference

XBUF

97

O

System clock (MCLK) or crystal clock (ACLK) output

Xin

99

I

Input port for crystal oscillator

Xout/TCLK

98

I/O

Output terminal of crystal oscillator or test clock input

detailed description

processing unit

The processing unit is based on a consistent and orthogonal designed CPU and instruction set. This design

structure results in a RISC-like architecture, highly transparent to the application development, which is

distinguished by ease of programming. All operations other than program-flow instructions consequently are

performed as register operations in conjunction with seven addressing modes for source and four modes for

destination operand.

CPU registers

The CPU has sixteen registers that provide

reduced instruction execution time. This reduces

the register-to-register operation execution time

to one cycle of the processor frequency.

Four of the registers are reserved for special use

as a program counter, a stack pointer, a status

register, and a constant generator. The remaining

registers are available as general-purpose regis-

ters.

Peripherals are connected to the CPU using a

data address and control bus and can be handled

easily with all instructions for memory manipula-

tion.

Program Counter

General-Purpose Register

PC/R0

Stack Pointer

SP/R1

Status Register

SR/CG1/R2

Constant Generator

CG2/R3

R4

General-Purpose Register

R5

General-Purpose Register

R14

General-Purpose Register

R15

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSP430F5342IRGZ | RISC MICROCONTROLLER, PQCC48 |

| MSP430F5341IRGZT | RISC MICROCONTROLLER, PQCC48 |

| MSP430F5514IRGC | 16-BIT, FLASH, 25 MHz, RISC MICROCONTROLLER, PQCC64 |

| MSP430F5528IRGC | 16-BIT, FLASH, 25 MHz, RISC MICROCONTROLLER, PQCC64 |

| MSP430F5522IRGC | 16-BIT, FLASH, 25 MHz, RISC MICROCONTROLLER, PQCC64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSP430C336PJM | 制造商:TI 制造商全稱:Texas Instruments 功能描述:MIXED SIGNAL MICROCONTROLLERS |

| MSP430C337 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:MIXED SIGNAL MICROCONTROLLERS |

| MSP430C337HFD | 制造商:TI 制造商全稱:Texas Instruments 功能描述:MIXED SIGNAL MICROCONTROLLERS |

| MSP430C337IPJM | 制造商:TI 制造商全稱:Texas Instruments 功能描述:MIXED SIGNAL MICROCONTROLLERS |

| MSP430C337PJM | 制造商:TI 制造商全稱:Texas Instruments 功能描述:MIXED SIGNAL MICROCONTROLLERS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。