- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄224506 > MT55L512V18PF-6 (CYPRESS SEMICONDUCTOR CORP) 512K X 18 ZBT SRAM, 3.5 ns, PBGA165 PDF資料下載

參數(shù)資料

| 型號(hào): | MT55L512V18PF-6 |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | SRAM |

| 英文描述: | 512K X 18 ZBT SRAM, 3.5 ns, PBGA165 |

| 封裝: | 13 X 15 MM, FBGA-165 |

| 文件頁(yè)數(shù): | 23/25頁(yè) |

| 文件大小: | 304K |

| 代理商: | MT55L512V18PF-6 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)當(dāng)前第23頁(yè)第24頁(yè)第25頁(yè)

7

8Mb: 512K x 18, 256K x 32/36 Pipelined ZBT SRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT55L512L18P_C.p65 – Rev. 2/02

2002, Micron Technology, Inc.

8Mb: 512K x 18, 256K x 32/36

PIPELINED ZBT SRAM

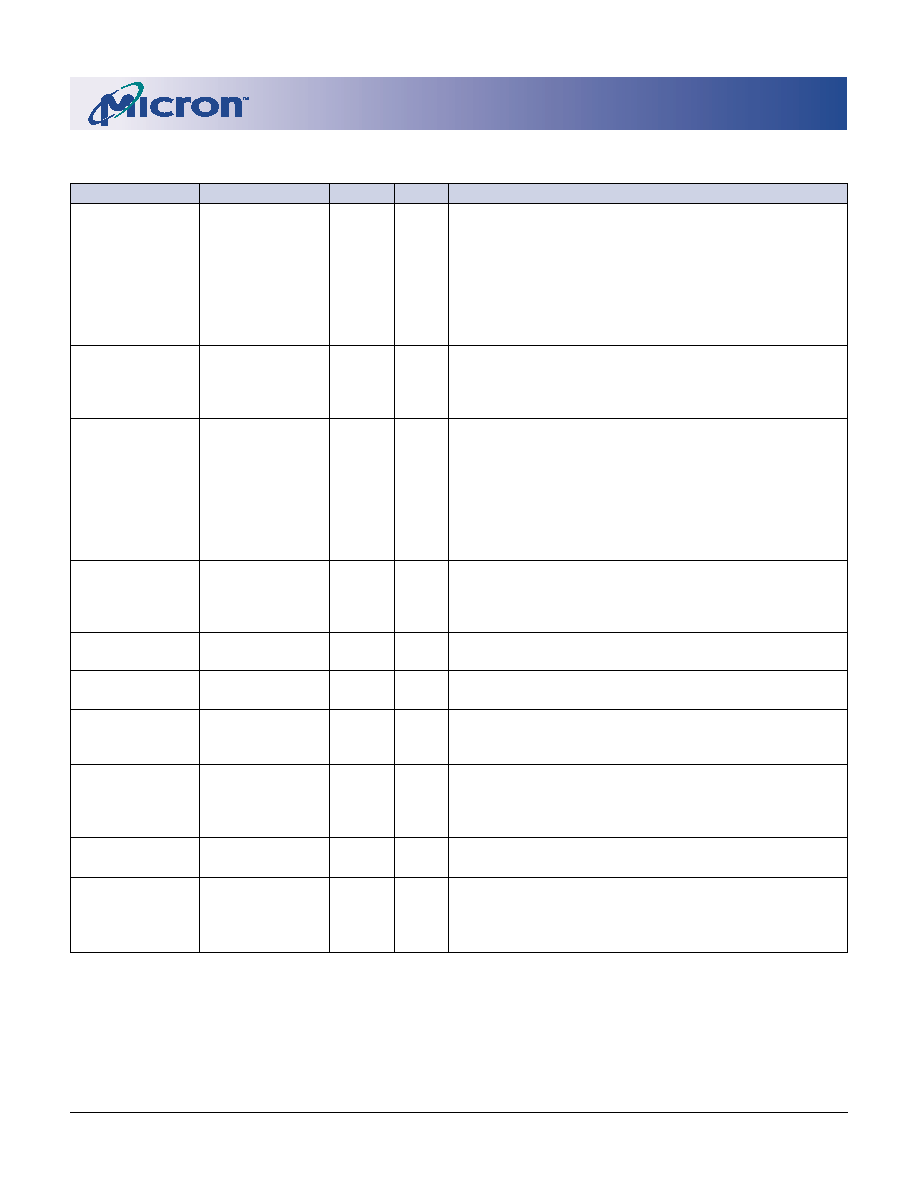

TQFP PIN DESCRIPTIONS (CONTINUED)

x18

x32/x36

SYMBOL TYPE

DESCRIPTION

88

R/W#

Input

Read/Write: This input determines the cycle type when

ADV/LD# is LOW and is the only means for determining

READs and WRITEs. READ cycles may not be converted into

WRITEs (and vice versa) other than by loading a new

address. A LOW on this pin permits BYTE WRITE operations

and must meet the setup and hold times around the rising

edge of CLK. Full bus-width WRITEs occur if all byte write

enables are LOW.

31

MODE

Input

Mode: This input selects the burst sequence. A LOW on

(LBO#)

this pin selects linear burst. NC or HIGH on this pin selects

interleaved burst. Do not alter input state while device is

operating. LBO# is the JEDEC-standard term for MODE.

(a) 58, 59, 62, 63,

(a) 52, 53, 56-59,

DQa

Input/

SRAM Data I/Os: Byte “a” is associated with DQa pins;

68, 69, 72-74

62, 63

Output

Byte “b” is associated with DQb pins; Byte “c” is

(b) 8, 9, 12, 13,

(b) 68, 69, 72-75,

DQb

associated with DQc pins; Byte “d” is associated with

18, 19, 22-24

78, 79

DQd pins. Input data must meet setup and hold times

(c) 2, 3, 6-9,

DQc

around the rising edge of CLK.

12, 13

(d) 18, 19, 22-25,

DQd

28, 29

n/a

51

NF/DQPa

NF/

No Function/Data Bits: On the x32 version, these pins are

80

NF/DQPb

I/O

No Function (NF) and can be left floating or connected to

1

NF/DQPc

GND to minimize thermal impedance. On the x36 version,

30

NF/DQPd

these bits are DQPs.

14, 15, 16, 41, 65,

VDD

Supply

Power Supply: See DC Electrical Characteristics and

66, 91

Operating Conditions for range.

4, 11, 20, 27,

VDDQ

Supply

Isolated Output Buffer Supply: See DC Electrical

54, 61, 70, 77

Characteristics and Operating Conditions for range.

5, 10, 17, 21,

VSS

Supply

Ground: GND.

26, 40, 55, 60,

67, 71, 76, 90

1-3, 6, 7, 25,

n/a

NC

–

No Connect: These pins can be left floating or connected

28-30, 51-53, 56,

to GND to minimize thermal impedance.

57, 75, 78, 79,

95, 96

38, 39, 42, 43

DNU

–

Do Not Use: These signals may either be unconnected or

wired to GND to minimize thermal impedance.

84

NF

–

No Function: This pin is internally connected to the die and

will have the capacitance of an input pin. It is allowable to

leave this pin unconnected or driven by signals. Pin 84 is

reserved as an address pin for the 18Mb ZBT SRAM.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT57W4MH9CF-6 | 4M X 9 DDR SRAM, 0.5 ns, PBGA165 |

| MT58L128L36D1T-5IT | 128K X 36 STANDARD SRAM, 2.8 ns, PQFP100 |

| MT58L128V36P1B-4 | 128K X 36 STANDARD SRAM, 2.3 ns, PBGA119 |

| MT58L32L36PT-7.5 | 32K X 36 CACHE SRAM, 4.2 ns, PQFP100 |

| MT58L512L18DS-7.5IT | 512K X 18 CACHE SRAM, 4 ns, PQFP100 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT55L512Y32PF-10 | 制造商:Micron Technology Inc 功能描述: |

| MT55L512Y32PT-10 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Micron Technology Inc 功能描述: |

| MT55L512Y32PT-6 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Micron Technology Inc 功能描述: |

| MT55L512Y32PT-7.5 | 制造商:Cypress Semiconductor 功能描述:512KX32 SRAM PLASTIC TQFP 3.3V |

| MT55L512Y36FT10 | 制造商:Micron Technology Inc 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。