- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367813 > PCD5002H (NXP SEMICONDUCTORS) Advanced POCSAG and APOC-1 Paging Decoder PDF資料下載

參數(shù)資料

| 型號(hào): | PCD5002H |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 尋呼電路 |

| 英文描述: | Advanced POCSAG and APOC-1 Paging Decoder |

| 中文描述: | TELECOM, PAGING DECODER, PQFP32 |

| 封裝: | 7 X 7 MM, 1.40 MM HEIGHT, PLASTIC, SOT-358-1, LQFP-32 |

| 文件頁(yè)數(shù): | 22/48頁(yè) |

| 文件大?。?/td> | 203K |

| 代理商: | PCD5002H |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)

1997 Jun 24

22

Philips Semiconductors

Product specification

Advanced POCSAG and APOC-1 Paging

Decoder

PCD5002

8.30

Real time clock

The PCD5002 provides a periodic reference pulse at

output REF. The frequency of this signal can be selected

by SPF programming:

32768 Hz

50 Hz (square-wave)

2 Hz

1

60

Hz.

The 32768 Hz signal does not have a fixed period, it

consists of 32 pulses distributed over 75 main oscillator

cycles at 76.8 kHz. The timing is illustrated in Fig.15.

When programmed for

1

60

Hz (1 pulse per minute) the

pulse at output REF is held off while the receiver is

enabled.

Except for the 50 Hz frequency the pulse width t

RFP

is

equal to one decoder clock period.

The real time clock counter runs continuously irrespective

of the operating condition of the PCD5002. It contains a

seconds register

(maximum 59) and a

1

100

second

register

(maximum 99), which can be read from or written

to via the I

2

C-bus. The bit allocation of both registers is

shown in Tables 19 and 20.

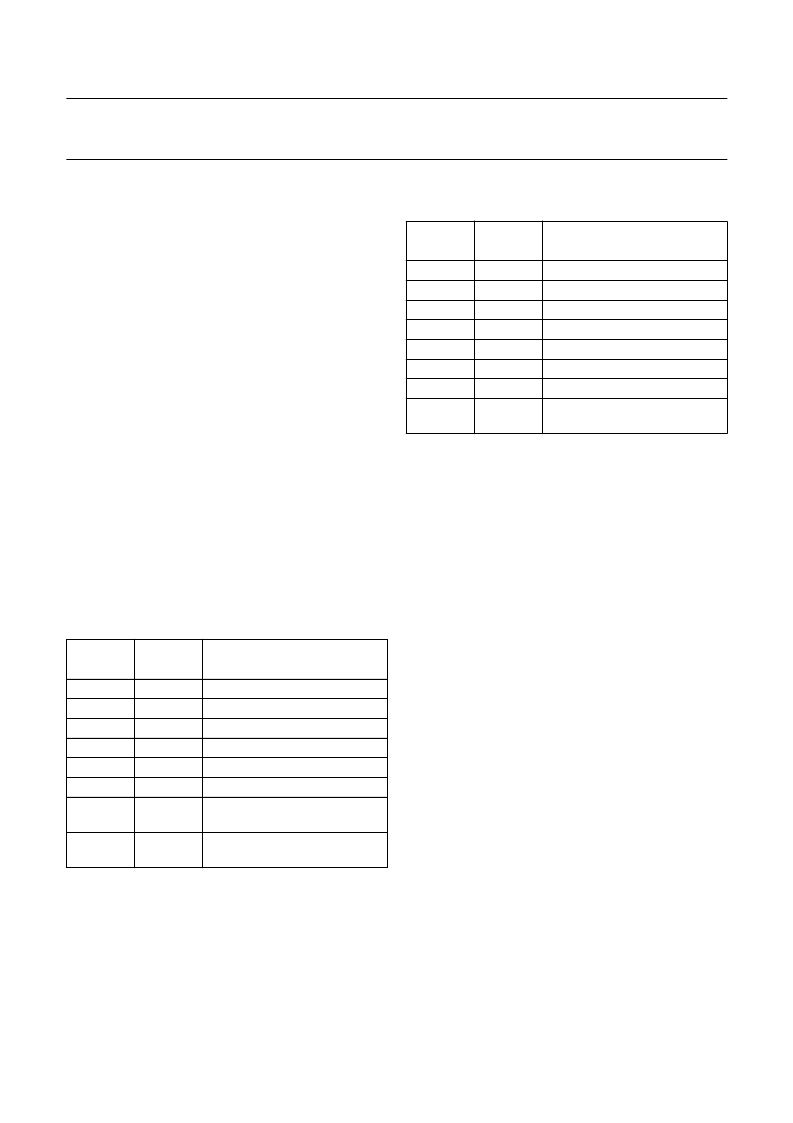

Table 19

Real time clock; seconds register (01H;

read/write)

BIT

(MSB D7)

VALUE

DESCRIPTION

D0

D1

D2

D3

D4

D5

D6

X

1 s

2 s

4 s

8 s

16 s

32 s

not used: ignored when written,

undetermined when read

not used: ignored when written,

undetermined when read

D7

X

Table 20

Real time clock;

1

100

second register (02H;

read/write)

8.31

Periodic interrupt

A periodic interrupt can be realised with the periodic

interrupt counter. This 8-bit counter is incremented every

1

100

s and produces an interrupt when it reaches the value

stored in the periodic interrupt modulus register.

The counter register is then reset and counting continues.

Operation is started by writing a non-zero value to the

modulus register. Writing a zero will stop interrupt

generation immediately and will halt the periodic interrupt

counter after 2.55 s.

The modulus register is write-only, the counter register is

read only. Both registers have the same index address

(05H).

8.32

Received call delay

Call reception (detection of an enabled RIC) causes both

the periodic interrupt modulus and the counter register to

be reset.

Since the periodic interrupt counter runs for another 2.55 s

after a reset, the received call delay (in

1

100

s units) can be

determined by reading the counter register.

BIT

(MSB D7)

VALUE

DESCRIPTION

D0

D1

D2

D3

D4

D5

D6

D7

X

0 01 s

0.02 s

0.04 s

0.08 s

0.16 s

0.32 s

0.64 s

not used: ignored when written,

undetermined when read

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCD5 | Fuse |

| PCB1 | Fuse |

| PCB2 | Fuse |

| PCB2.5 | Fuse |

| PCB3 | Fuse |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCD5002HBD-S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication Decoder |

| PCD5002HBD-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication Decoder |

| PCD5002U/10 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Advanced POCSAG and APOC-1 Paging Decoder |

| PCD5003 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Advanced POCSAG Paging Decoder |

| PCD5003A | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Enhanced Pager Decoder for POCSAG |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。