- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄367813 > PCD5002H (NXP SEMICONDUCTORS) Advanced POCSAG and APOC-1 Paging Decoder PDF資料下載

參數(shù)資料

| 型號(hào): | PCD5002H |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 尋呼電路 |

| 英文描述: | Advanced POCSAG and APOC-1 Paging Decoder |

| 中文描述: | TELECOM, PAGING DECODER, PQFP32 |

| 封裝: | 7 X 7 MM, 1.40 MM HEIGHT, PLASTIC, SOT-358-1, LQFP-32 |

| 文件頁(yè)數(shù): | 30/48頁(yè) |

| 文件大小: | 203K |

| 代理商: | PCD5002H |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)當(dāng)前第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)

1997 Jun 24

30

Philips Semiconductors

Product specification

Advanced POCSAG and APOC-1 Paging

Decoder

PCD5002

8.57

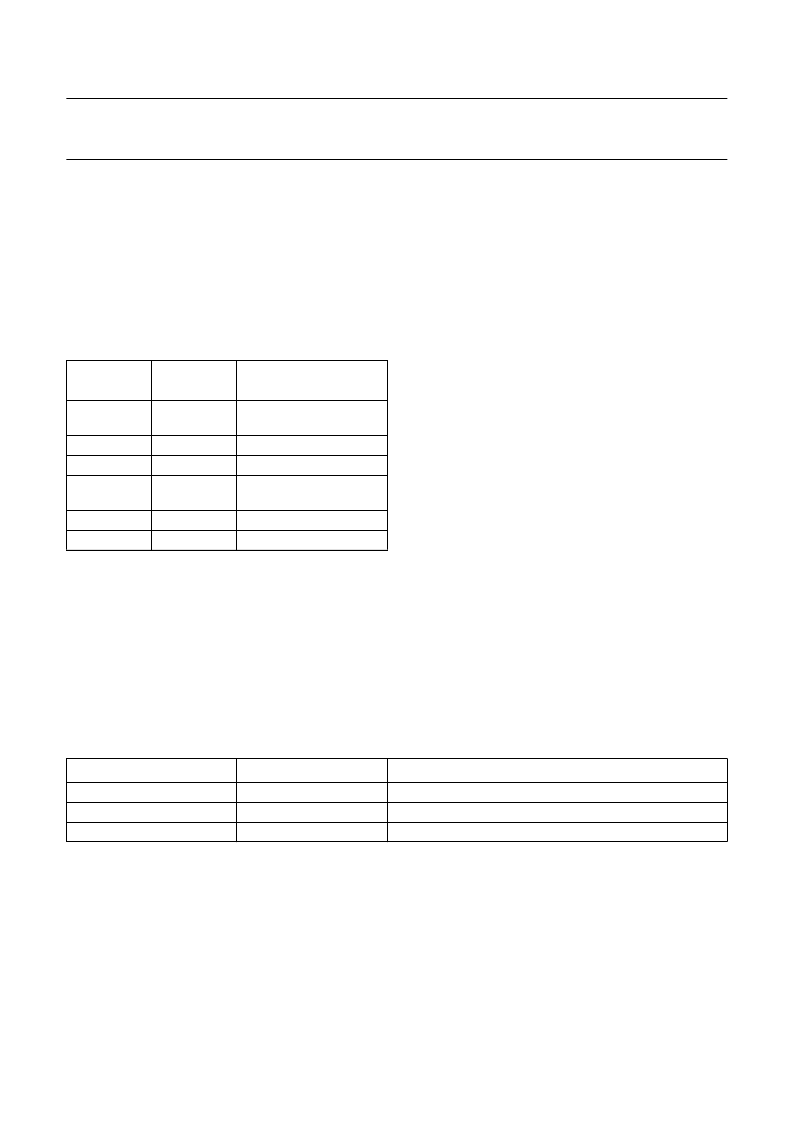

Synthesizer programming data

Data for programming a PLL synthesizer via pins ZSD,

ZSC and ZLE can be stored in row 1 of the EEPROM.

Six bytes are available starting with address 08H.

Data is transferred in two serial blocks of 24 bits each,

starting with bit 0 (MSB) of block 1. Any unused bits must

be programmed at the beginning of a block.

Table 28

Synthesizer programming data (EEPROM

address 08H to 0DH)

8.58

Identifier storage allocation

Up to 6 different identifiers can be stored in EEPROM for

matching with incoming data. The PCD5002 can

distinguish two types of identifiers:

User addresses (RIC)

User Programmable Sync Words (UPSW)

Batch zero identifiers

Continuous data decoding (CDD) sync words.

ADDRESS

(HEX)

BIT

(MSB: D7)

DESCRIPTION

08

D7 to D0

bits 0 to 7 of data

block 1 (bit 0 is MSB)

bits 8 to 15

bits 16 to 23

bits 0 to 7 of data

block 2 (bit 0 is MSB)

bits 8 to 15

bits 16 to 23

09

0A

0B

D7 to D0

D7 to D0

D7 to D0

0C

0D

D7 to D0

D7 to D0

Identifiers are stored in EEPROM rows 2, 3 and 4. Each

identifier location consists of 3 bytes in the same column.

The identifier number is equal to the column number + 1.

Each identifier can be individually enabled. The standard

POCSAG sync word is always enabled and has identifier

number 7.

The identifier type is determined by bits D2 and D0 of

identifier byte 3, as shown in Table 31.

Identifiers 1 and 2 always represent RICs or batch zero

identifiers. The last 4 identifiers (numbers 3 to 6) can

represent any identifier type.

A UPSW represents an unused address and must differ by

more than 6 bits from preamble to guarantee detection.

A batch zero identifier marks the start of a new cycle in the

APOC-1 protocol. It is only recognized when APOC-1

decoding has been enabled (SPF byte 00, bit D0).

Reception of a CDD sync word initiates continuous data

decoding. CDD sync words are only recognized when

continuous data decoding has been enabled (SPF

byte 00, bit 6).

Table 29 shows the memory locations of the 6 identifiers.

The bit allocation per identifier is given in Table 30.

Table 29

Identifier storage allocation (EEPROM address 10H to 25H)

ADDRESS (HEX)

BYTE

DESCRIPTION

10 to 15

18 to 1D

20 to 25

1

2

3

identifier number 1 to 6

identifier number 1 to 6

identifier number 1 to 6

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCD5 | Fuse |

| PCB1 | Fuse |

| PCB2 | Fuse |

| PCB2.5 | Fuse |

| PCB3 | Fuse |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCD5002HBD-S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication Decoder |

| PCD5002HBD-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication Decoder |

| PCD5002U/10 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Advanced POCSAG and APOC-1 Paging Decoder |

| PCD5003 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Advanced POCSAG Paging Decoder |

| PCD5003A | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Enhanced Pager Decoder for POCSAG |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。