- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369993 > pentium pro processor (Intel Corp.) Pentium Pro Processor with 1MB L2 Cache at 200MHZ(1兆比特L2高速緩存頻率200兆赫茲處理器) PDF資料下載

參數(shù)資料

| 型號: | pentium pro processor |

| 廠商: | Intel Corp. |

| 英文描述: | Pentium Pro Processor with 1MB L2 Cache at 200MHZ(1兆比特L2高速緩存頻率200兆赫茲處理器) |

| 中文描述: | 奔騰Pro處理器在200MHz(1兆比特二級高速緩存頻率200兆赫茲處理器帶有1MB的L2緩存) |

| 文件頁數(shù): | 30/39頁 |

| 文件大小: | 930K |

| 代理商: | PENTIUM PRO PROCESSOR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

AP-523

E

30

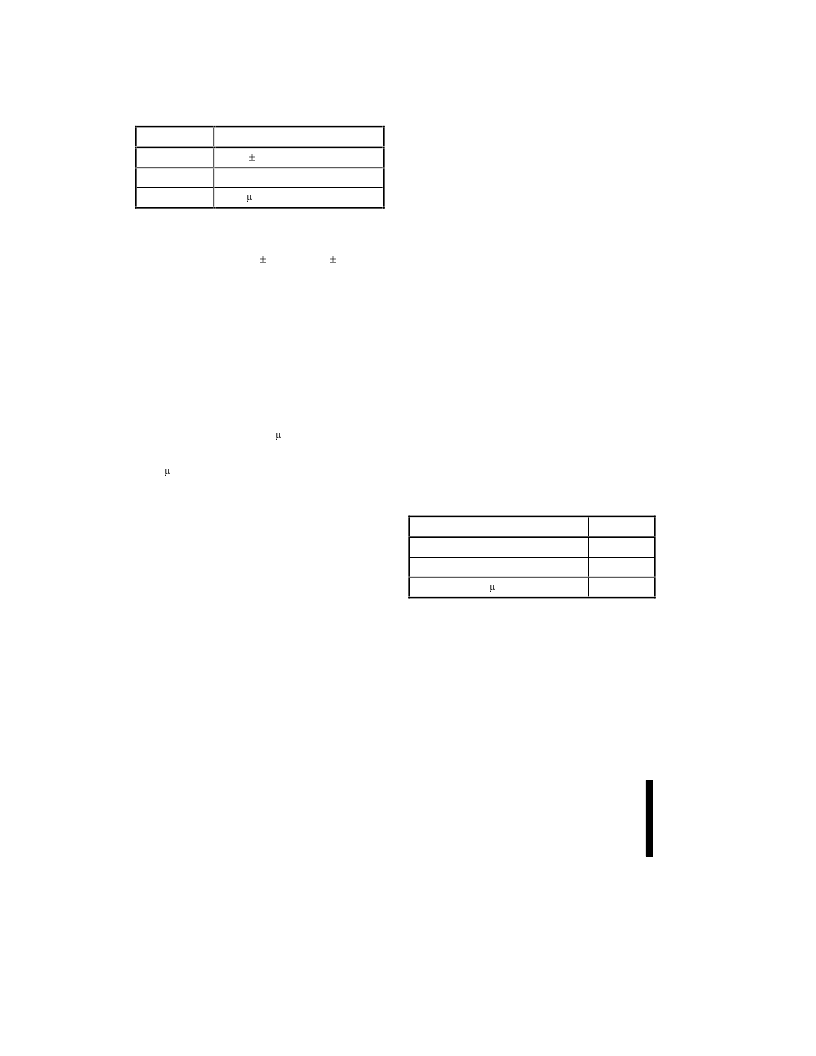

Table 6. 150 MHz, 256-Kbyte L2 Cache Pentium

Pro

Processor Voltage and Current

Specifications

Parameter

Value

Voltage

3.1V

±

5%

Current

0.3 - 9.9A

Slew rate

30A/

m

s at converter pins

10.1.1.

INPUT VOLTAGES

Available inputs are at 12V

±

5% and at 5V

±

5%. Either

one or both of these inputs may be used by the converter.

The vendor must provide maximum current loading

requirements on all inputs. These voltages are supplied

by a conventional PC power supply through a cable to

the motherboard.

Load Transient Effects on

Input Voltages

GUIDELINE

The converter must be able to provide for an output

current step at the load from I

MIN

to I

PEAK

(per Table 7)

in 360 ns. During this step response the input current

di/dt must not exceed 0.1 Amps/

m

s. For applications with

multiple converters, it is recommended that the step

response di/dt of an individual converter not exceed 0.04

Amps/

m

s.

10.1.2.

I/O CONTROLS

These are signals that control the DC-to-DC converter or

provide feedback from the DC-to-DC converter (shown

with corresponding pins in Table 10). Input and output

levels must be consistent with TTL DC specifications.

Power-Good (PWRGD)

GUIDELINE

An open collector signal must be provided. When the

output voltage is not within specifications (nominal or

selected voltage ±10%) this signal must be at the low

state. This signal must transition to the proper state

within 5 milliseconds of the output coming into or going

out of its specified range.

Output Enable (OUTEN)

GUIDELINE

The module must accept an open collector signal for

controlling the output voltage: The low state must disable

the output voltage. When disabled, the PWRGD output

must be in the low state.

Upgrade Present (UP#)

EXPECTED

The module must accept an open collector signal, used to

indicate the presence of an upgrade processor. Typical

state is high (standard processor in system). When in the

low or ground state (OverDrive processor in system) the

output voltage must be disabled unless the converter can

supply to an OverDrive processor’s specifications (see

Table 8). When disabled, the PWRGD output must be in

the low state.

Voltage Identification (VID[0:3])

EXPECTED

The module must accept four signals, used to indicate the

voltage required by the processor, as defined by Table 9.

10.1.3.

OUTPUT REQUIREMENTS

DC Output Current

REQUIRED

The DC output current requirements corresponding to the

processor in Table 6 are shown in Table 7.

Table 7. DC Output Current

Parameter

Value

I

MIN

0.3 Amps

I

MAX

9.9 Amps

I

PEAK

(Several

m

s of overshoot)

11 Amps

Voltage Range by Application

EXPECTED

A Pentium Pro processor-based system may require one

of the adjustment ranges shown in Table 8. The I

CC

column represents the current requirement Intel expects

for processors at each voltage.

Processor Voltage Identification

EXPECTED

The adjustment mechanism must be by four binary

weighted inputs using the coding described in Table 9.

相關PDF資料 |

PDF描述 |

|---|---|

| pentium processor with MMX | 32-bit processor with MMX technology(32位帶MMX技術處理器) |

| pentium processor | 32 Bit Processor With MMX And Mobile Module(32位帶移動模塊和MMX技術CPU) |

| PESD0603-140 | Raychem Overvoltage Devices |

| PESD5V2S18U | ESD protection array |

| PESDXL4UW | Low capacitance quadruple ESD protection array |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| P-ENV568K3G3 | 制造商:Panasonic Industrial Company 功能描述:TUNER |

| PEO14012 | 制造商:TE Connectivity 功能描述:RELAY SPCO 12VDC |

| PEO14024 | 制造商:TE Connectivity 功能描述:RELAY SPCO 24VDC |

| PEO96742 | 制造商:Delphi Corporation 功能描述:ASM TERM |

| PEOODO3A | 制造商:MACOM 制造商全稱:Tyco Electronics 功能描述:Versatile Power Entry Module with Small Footprint |

發(fā)布緊急采購,3分鐘左右您將得到回復。