- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378205 > RTL8139A (Electronic Theatre Controls, Inc.) REALTEK SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT PDF資料下載

參數(shù)資料

| 型號(hào): | RTL8139A |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | REALTEK SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| 中文描述: | 瑞昱單芯片快速以太網(wǎng)控制器電源管理 |

| 文件頁(yè)數(shù): | 10/62頁(yè) |

| 文件大小: | 648K |

| 代理商: | RTL8139A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)

RTL8139C(L)

2002/01/10

Rev.1.4

10

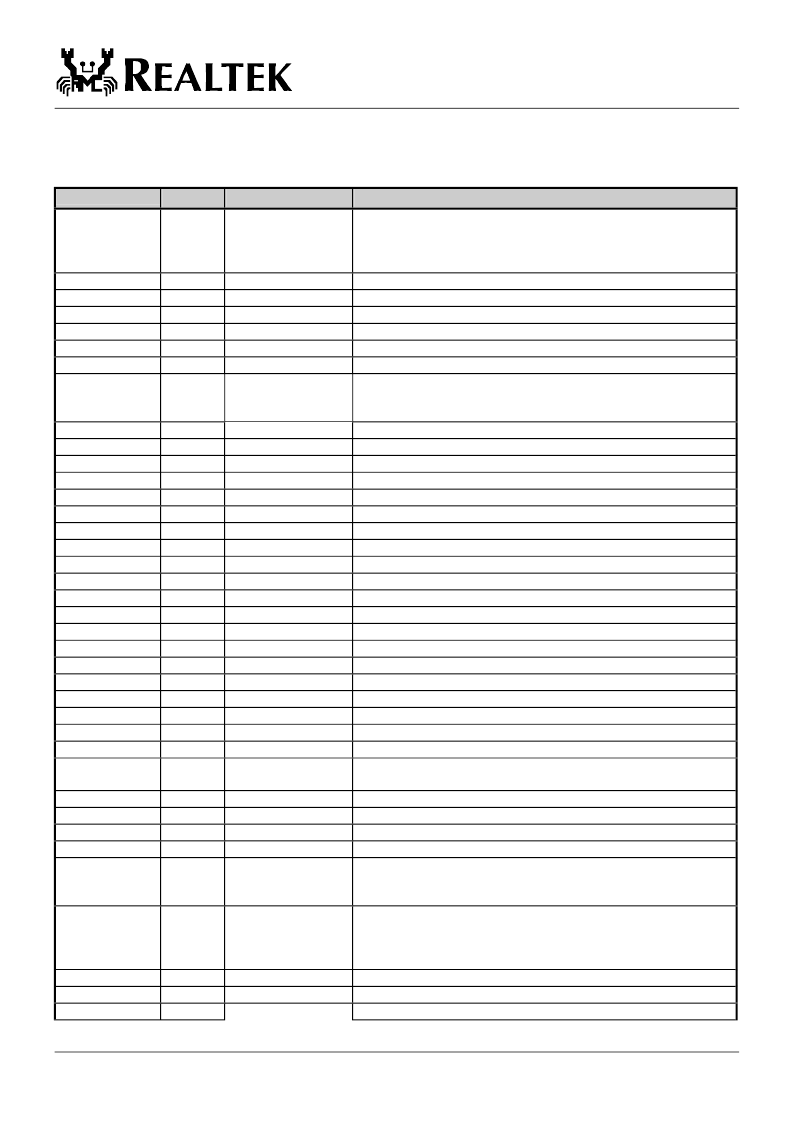

6. Register Descriptions

The RTL8139C(L) provides the following set of operational registers mapped into PCI memory space or I/O space.

Offset

0000h

R/W

R/W

Tag

IDR0

Description

ID Register 0:

The ID registers 0-5 are only permitted to read/write

by 4-byte access. Read access can be byte, word, or double word

access. The initial value is autoloaded from the EEPROM EthernetID

field.

ID Register 1

ID Register 2

ID Register 3

ID Register 4

ID Register 5

Reserved

Multicast Register 0:

The MAR registers 0-7 are only permitted to

read/write by 4-byte access. Read access can be byte, word, or double

word access. Driver is responsible for initializing these registers.

Multicast Register 1

Multicast Register 2

Multicast Register 3

Multicast Register 4

Multicast Register 5

Multicast Register 6

Multicast Register 7

Transmit Status of Descriptor 0

Transmit Status of Descriptor 1

Transmit Status of Descriptor 2

Transmit Status of Descriptor 3

Transmit Start Address of Descriptor0

Transmit Start Address of Descriptor1

Transmit Start Address of Descriptor2

Transmit Start Address of Descriptor3

Receive (Rx) Buffer Start Address

Early Receive (Rx) Byte Count Register

Early Rx Status Register

Command Register

Current Address of Packet Read

(The initial value is 0FFF0h)

Current Buffer Address:

The initial value is 0000h. It reflects total

received byte-count in the rx buffer.

Interrupt Mask Register

Interrupt Status Register

Transmit (Tx) Configuration Register

Receive (Rx) Configuration Register

Timer Count Register:

This register contains a 32-bit

general-purpose timer. Writing any value to this 32-bit register will

reset the original timer and begin to count from zero.

Missed Packet Counter:

Indicates the number of packets discarded

due to rx FIFO overflow. It is a 24-bit counter. After s/w reset, MPC is

cleared. Only the lower 3 bytes are valid.

When any value is written, MPC will be reset also.

93C46 (93C56) Command Register

Configuration Register 0

Configuration Register 1

0001h

0002h

0003h

0004h

0005h

R/W

R/W

R/W

R/W

R/W

-

R/W

IDR1

IDR2

IDR3

IDR4

IDR5

-

MAR0

0006h-0007h

0008h

0009h

000Ah

000Bh

000Ch

000Dh

000Eh

000Fh

0010h-0013h

0014h-0017h

0018h-001Bh

001Ch-001Fh

0020h-0023h

0024h-0027h

0028h-002Bh

002Ch-002Fh

0030h-0033h

0034h-0035h

0036h

0037h

0038h-0039h

003Ah-003Bh

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R

R

R/W

R/W

R

MAR1

MAR2

MAR3

MAR4

MAR5

MAR6

MAR7

TSD0

TSD1

TSD2

TSD3

TSAD0

TSAD1

TSAD2

TSAD3

RBSTART

ERBCR

ERSR

CR

CAPR

CBR

003Ch-003Dh

003Eh-003Fh

0040h-0043h

0044h-0047h

0048h-004Bh

R/W

R/W

R/W

R/W

R/W

IMR

ISR

TCR

RCR

TCTR

004Ch-004Fh

R/W

MPC

0050h

0051h

0052h

R/W

R/W

R/W

9346CR

CONFIG0

CONFIG1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RTL8139B | REALTEK SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139D | REALTEK SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8201 | REALTEK SINGLE CHIP SINGLE PORT 10/100M FAST ETHERNET PHYCEIVER RTL8201BL |

| RTL8201BL | REALTEK SINGLE CHIP SINGLE PORT 10/100M FAST ETHERNET PHYCEIVER RTL8201BL |

| RTL8208 | REALTEK SINGLE CHIP OCTAL 10/100 MBPS FAST ETHERNET TRANSCEIVER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RTL8139B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:REALTEK SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:REALTEK SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139C_PLUS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:RTL8139C_Plus Specification |

| RTL8139CL | 制造商:Realtek Semiconductor 功能描述: |

| RTL8139CL+ | 制造商:Realtek Semiconductor 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。