- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄372108 > SAA2502 (NXP Semiconductors N.V.) ISO/MPEG Audio Source Decoder PDF資料下載

參數(shù)資料

| 型號(hào): | SAA2502 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | ISO/MPEG Audio Source Decoder |

| 中文描述: | 的ISO / MPEG音頻信源解碼器 |

| 文件頁(yè)數(shù): | 17/64頁(yè) |

| 文件大?。?/td> | 318K |

| 代理商: | SAA2502 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)

1997 Nov 17

17

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

7.4.2

M

ASTER INPUT MODE BIT RATE GENERATION

When master input mode is used, the SAA2502 fetches

input data at the effective bit rate. However after a hard

reset the input requests input data at the default bit rate

until synchronization has been established as shown in

Table 7.

When the clock generator mode is ‘free running internal

sample clock’ or ‘locked internal sample clock’ the default

input bit rate is always 384 kbits/s. When the mode is

‘external sample clock’ the SAA2502 derives the selected

bit rate from the signal FSCLKIN. But initially it has no

indication of the current sampling rate corresponding to

FSCLKIN. Therefore the bit rate of 384 kbits/s is

generated at an assumed sampling frequency of 44.1 kHz.

For different sample rates, the bit rate changes

proportionally.

The consequence is that while the SAA2502 is

synchronizing after a hard reset, the application should be

able to supply input data at the given default bit rate until

synchronization is established. Alternatively there is also

the possibility to overrule default bit rate setting and

sample rate setting using the control interface while

synchronization has not been established.

The speed at which input data is requested by the input in

master mode is changed in one of the following events:

When input synchronization is established at the end of

the verification phase and the bit rate index of the

decoded bit stream indicates a bit rate different from the

one currently selected. In this event, the bit rate is

adapted to the new index.

When the signal STOP is raised while the STOPRQ

control flag = logic 1, input requesting is halted.

Requesting resumes at the last selected input bit rate

when the STOP signal is dropped.

In all other events (including when the SAA2502 loses

synchronization), the last selected input bit rate is

maintained.

Whenever the selected bit rate changes while dynamic bit

rate is not enabled, the SAA2502 will generate internally a

soft reset resulting in a soft mute of the output interfaces

and a decoder restart in order to re-initialize internal buffer

settings.

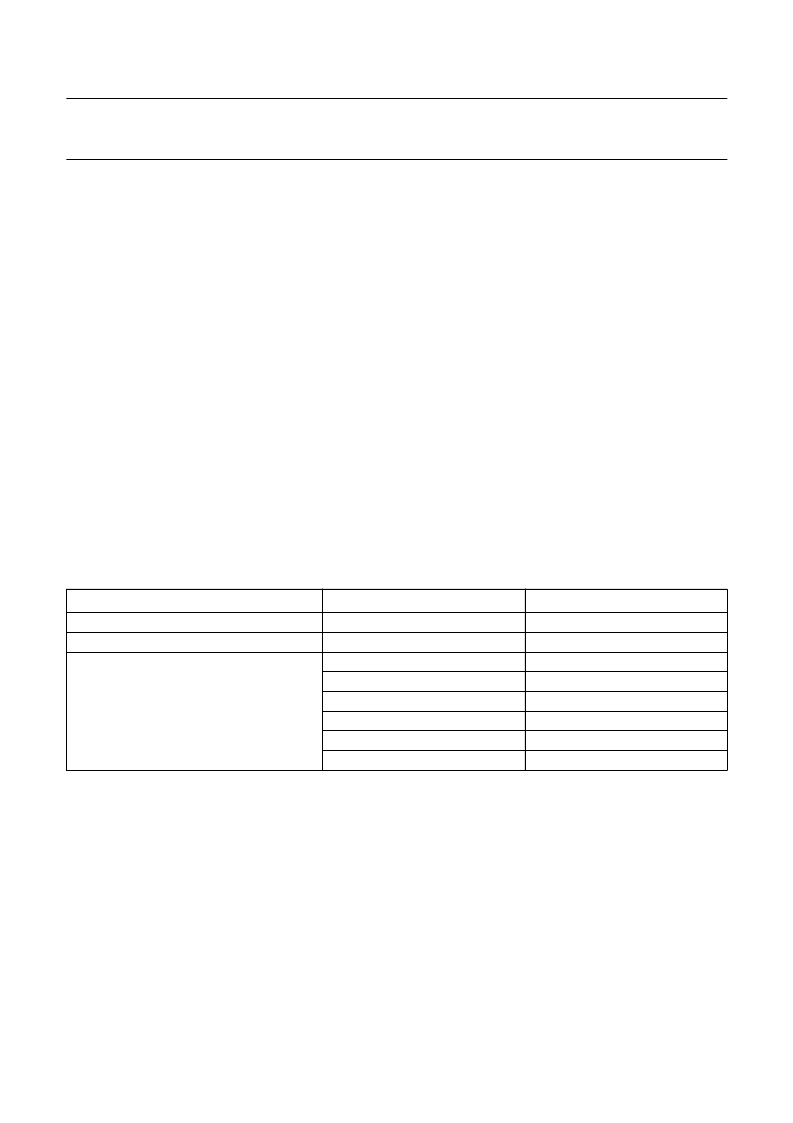

Table 7

Establishment of default bit rate

CLOCK GENERATOR MODE

FSCLKIN (kHz)

DEFAULT BIT RATE (kbits/s)

Free running internal clock

Locked internal clock

External sample clock

don’t care

don’t care

256 or 384

×

48

256 or 384

×

44.1

256 or 384

×

32

256 or 384

×

24

256 or 384

×

22.05

256 or 384

×

16

384

384

417.96

384

278.64

208.98

192

139.32

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA2502H | ISO/MPEG Audio Source Decoder |

| SAA2503 | MPEG2 audio decoder(MPEG2 音頻譯碼器) |

| SAA2503HT | MPEG2 audio decoder |

| SAA2505H-M1 | Digital multi-channel audio IC DUET |

| SAA2505 | Digital multi-channel audio IC DUET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA2502H | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:ISO/MPEG Audio Source Decoder |

| SAA2503 | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:MPEG2 audio decoder |

| SAA2503HT | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:MPEG2 audio decoder |

| SAA2505 | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:Digital multi-channel audio IC DUET |

| SAA2505H | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:Digital multi-channel audio IC DUET |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。