- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376341 > SCM69C233 (Motorola, Inc.) 4K x 64 Content Addressable Memory(4K x 64內(nèi)容可尋址存儲器) PDF資料下載

參數(shù)資料

| 型號: | SCM69C233 |

| 廠商: | Motorola, Inc. |

| 英文描述: | 4K x 64 Content Addressable Memory(4K x 64內(nèi)容可尋址存儲器) |

| 中文描述: | 4K的× 64內(nèi)容可尋址存儲器(4K的× 64內(nèi)容可尋址存儲器) |

| 文件頁數(shù): | 11/22頁 |

| 文件大小: | 167K |

| 代理商: | SCM69C233 |

MCM69C233

SCM69C233

11

MOTOROLA FAST SRAM

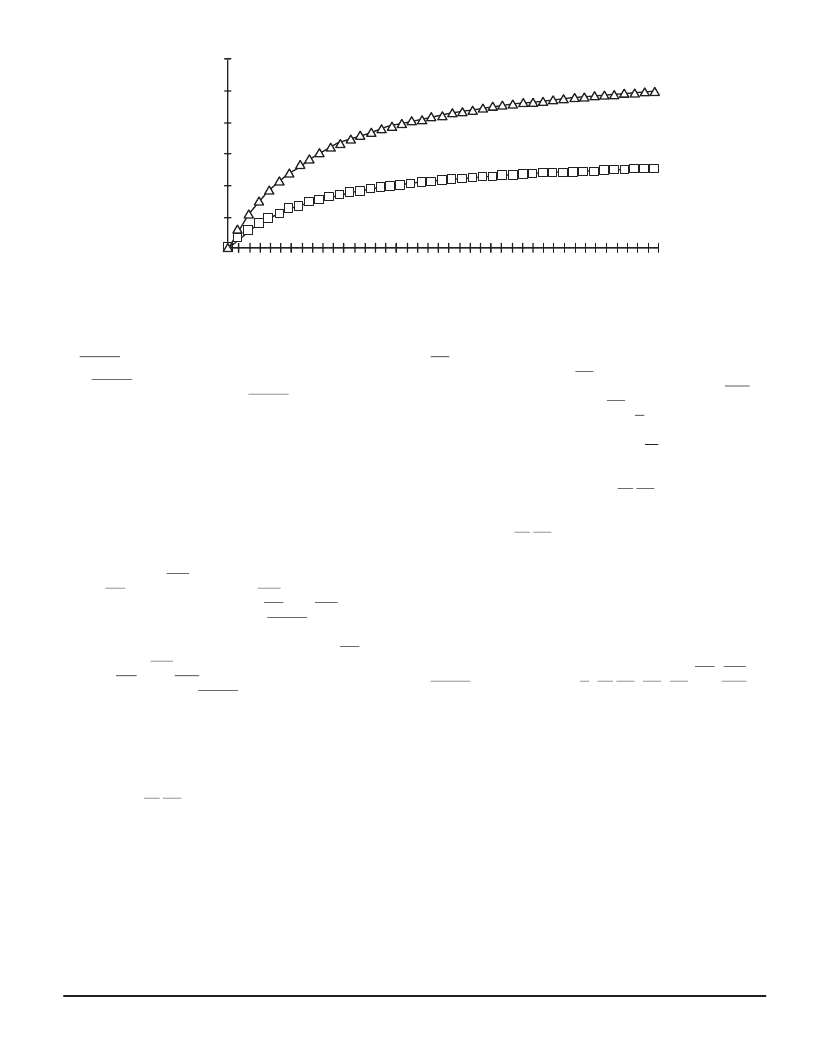

Figure 3. Connections per Second vs Match Cycle Time

MATCH CYCLE TIME IN CLOCK CYCLES

0

2,000

4,000

6,000

8,000

10,000

12,000

I

TYPICAL

WORST CASE

16

26

36

46

56

66

76

86

96

P

RESET

RESET is synchronous to the rising edge of the clock with

0 ns setup and hold. Asserting RESET for two clock cycles

removes all entries from the CAM table and entry queue. The

flag register is set to 1C16 (setting the queue empty,

buffered–entry mode, and table initialized bits). The error

register is set to FFFF16, indicating no errors. The interrupt

mask is cleared, and the almost–full register is set to FFF16.

TIMING OVERVIEW

CONTROL PORT

The control port of the MCM69C233 is asynchronous.

Data transfers, both read and write, are initiated by the

assertion of the SEL signal. Address values should be valid

and WE should be high, when SEL is asserted to begin

a read cycle. All values (address, WE, and SEL) should be

held until the MCM69C233 asserts DTACK to signal the end

of the read cycle.

Address and data values should be valid and WE should

be low, when SEL is asserted to begin a write cycle. Address,

data, WE, and SEL values should be held until the

MCM69C233 asserts DTACK to signal the end of the write

cycle.

MATCH PORT

The MCM69C233 match port is synchronous in operation.

When the match width is

≤

32 bits, a match cycle can be initi-

ated by presenting the match data on MQ31 – MQ0 and as-

serting the LH/SM signal with the appropriate setup time

relative to the rising edge of the clock. The assertion of the

MC output signifies the completion of the match cycle. If a

match has been found, the MS output is also asserted. If the

match is a virtual path circuit match in ATM mode, the VPC

output will be asserted with the MS output. Output data, if

any, is enabled by the assertion of the G input.

If the match width is greater than 32 bits, the lower bits are

first latched into the MCM69C233 by the LL input. The match

cycle is then initiated as specified in the previous paragraph.

Two alternative timing diagrams are presented to describe

the Match Port timing. In the first, LH/SM must meet setup

and hold specs across two consecutive clock cycles, while

the MQ bus need only be valid for a single cycle. In the se-

cond diagram, LH/SM need only be asserted for a single

clock cycle, while the MQ bus must be held valid with

constant data across two clock cycles.

DEPTH EXPANSION

Multiple CAMs can be cascaded to increase the depth of

the match table. The hardware requirements are very

straightforward, as the following pins on each device are sim-

ply wired in parallel: A2 – A0, DQ15 – DQ0, WE, IRQ,

DTACK, MQ31 – MQ0, K, G, LH/SM, MC, MS, and VPC.

Four CAMs can be easily cascaded. Simulations show that

eight devices can be cascaded if care is taken to minimize

the length of the PC board traces connecting the CAMs.

The buffered–entry mode prevents multiple matching en-

tries in a single CAM. The check for value instruction should

be used to verify that multiple matching entries will not result

from a potential new entry. If a match is found in CAM 1, for

example, the new value should be placed in CAM 1, where it

will replace the existing entry.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SCM69C432 | 16K x 64Content Addressable Memory(16K x 64內(nèi)容可尋址存儲器) |

| SCM69C433 | A Flexible Content-Addressable Memory (16K x 64 CAM)(1M內(nèi)容可尋址存儲器) |

| SD1012-03 | Side Door Adapter |

| SD1013-03 | RF MICROWAVE TRANSISTORS 108-152 MHZ APPLICATIONS |

| SD1013-3 | RF & MICROWAVE TRANSISTORS 108-152 MHz APPLICATIONS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SCM69C233TQ15 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| SCM69C433 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:16K x 64 CAM |

| SCM69C433TQ15 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:16K x 64 CAM |

| SCM69C433TQ15R | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:16K x 64 CAM |

| SCM8245ALVV400D | 制造商:Freescale Semiconductor 功能描述:INTEGEATED HOST PROC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。