- 您現在的位置:買賣IC網 > PDF目錄371179 > T7121 T7121 HDLC Interface for ISDN PDF資料下載

參數資料

| 型號: | T7121 |

| 英文描述: | T7121 HDLC Interface for ISDN |

| 中文描述: | T7121的HDLC接口用于ISDN |

| 文件頁數: | 44/68頁 |

| 文件大?。?/td> | 685K |

| 代理商: | T7121 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁當前第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

44

Lucent Technologies Inc.

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

Functional Description

(continued)

* In transparent mode (TRANS, AR11—B6 = 1), TDONE defaults to 1 when a transmitter reset (TRES, R6—B5 = 1) is performed.

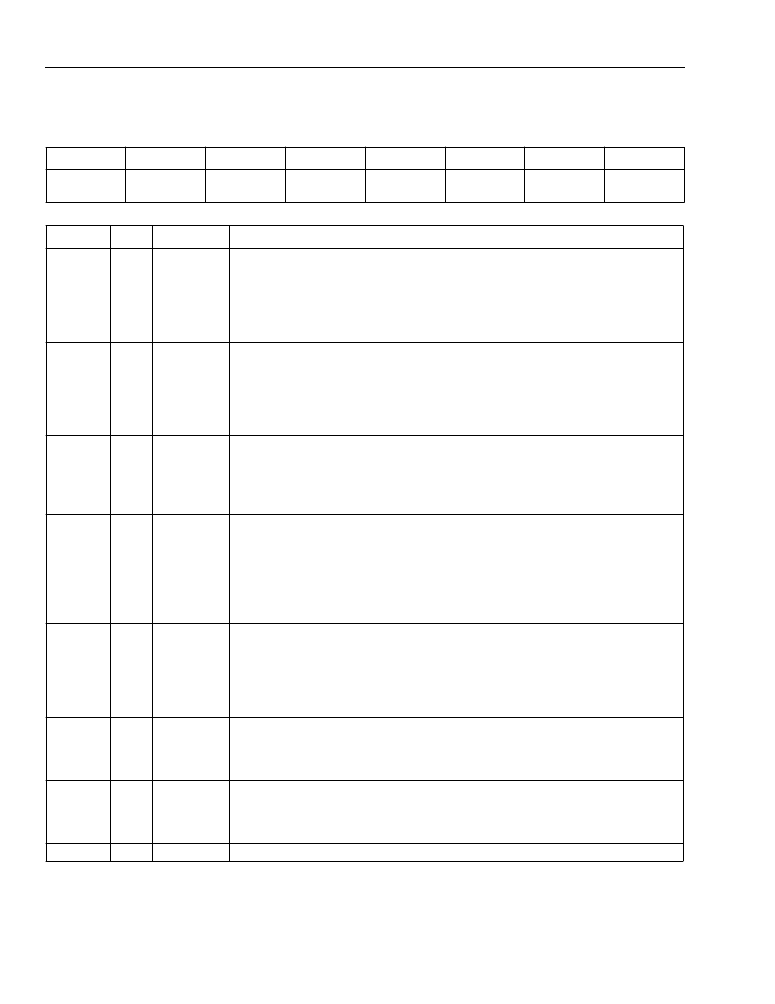

Table 25. Register R15—Interrupt Status Register

R15—B7

0

(–)

R15—B6

RIDL

(0)

R15—B5

OVERUN

(0)

R15—B4

REOF

(0)

R15—B3

RF

(0)

R15—B2

UNDABT

(0)

R15—B1

TE

(1)

R15—B0

TDONE

(0)*

Register

R15

Bit

B0

Symbol

TDONE

Name/Function

Transmit Done.

This status bit is set to 1 when transmission of the current

HDLC frame has been completed, either after the last bit of the closing flag or

after the last bit of an abort sequence. In the transparent mode (AR11—B6 = 1),

this status bit is set when the transmit FIFO is completely empty. A hardware

interrupt is generated only if the corresponding interrupt-enable bit (R14—B0) is

set. This status bit is cleared to 0 by a read of register 15.

Transmitter Empty.

If this bit is set to 1, the HDLC transmit FIFO is at or below

the programmed depth (see register 1). A hardware interrupt is generated only if

the corresponding interrupt-enable bit (R14—B1) is set. If DINT (R0—B0) is 0,

this status bit is cleared by a read of register 15. If DINT (R0—B0) is set to 1,

this bit actually represents the dynamic transmit empty condition, and is cleared

to 0 only when the transmit FIFO is loaded above the programmed empty level.

Underrun Abort.

A 1 indicates that an abort was transmitted because of a

transmit FIFO underrun. A hardware interrupt is generated only if the corre-

sponding interrupt-enable bit (R14—B2) is set. This status bit is cleared to 0 by

a read of register 15. This bit must be cleared to 0 before further transmission of

data is allowed. This interrupt is not generated in transparent mode.

Receiver Full.

This bit is set to 1 when the receive FIFO is at or above the pro-

grammed full level (see register 5). A hardware interrupt is generated if the cor-

responding interrupt-enable bit (R14—B3) is set. If DINT (R0—B0) is 0, this

status bit is cleared to 0 by a read of register 15. If DINT (R0—B0) is set to 1,

then this bit actually represents the dynamic receive-full condition and is cleared

only when the receive FIFO is read (or emptied) below the programmed full

level.

Receive End-of-Frame.

This bit is set to 1 when the receiver has finished

receiving a frame. It becomes 1 upon reception of the last bit of the closing flag

of a frame or the last bit of an abort sequence. A hardware interrupt is generated

only if the corresponding interrupt-enable bit (R14—B4) is set. This status bit is

cleared to 0 by a read of register 15. This bit is not generated in transparent

mode.

Receiver Overrun.

This bit is set to 1 when the receive FIFO has overrun its

capacity. A hardware interrupt is generated only if the corresponding interrupt-

enable bit (R14—B5) is set. This status bit is cleared to 0 by a read of register

15.

Receiver Idle.

This bit is set to 1 when the HIFI-64 HDLC receiver is idle (i.e.,

15 or more consecutive 1s have been received). A hardware interrupt is gener-

ated only if the corresponding interrupt-enable bit (R14—B6) is set. This status

bit is cleared to 0 by a read of register 15.

RESERVED Program to 0.

R15

B1

TE

R15

B2

UNDABT

R15

B3

RF

R15

B4

EOF

R15

B5

OVERUN

R15

B6

RIDL

R15

B7

相關PDF資料 |

PDF描述 |

|---|---|

| T7121-EL2 | T7121 HDLC Interface for ISDN |

| T7121-PL2 | T7121 HDLC Interface for ISDN |

| T7121 | HDLC Interface for ISDN (HIFI-64)(應用于ISDN的HDLC(高階數據鏈路)接口) |

| T7502 | T7502 Dual PCM Codec with Filters |

| T7503 | T7503 Dual PCM Codec with Filters |

相關代理商/技術參數 |

參數描述 |

|---|---|

| T7-121A1 | 制造商:OTTO 功能描述:Toggle Switches ON NONE OFF 1 Pole Standard Bat Handle 制造商:OTTO Engineering Inc 功能描述:Switch Toggle ON None OFF SPST Bat Toggle Screw 16A 115VAC 28VDC Panel Mount with Threads |

| T7-121A2D | 制造商:OTTO 功能描述:Toggle Switches ON NONE OFF 1 Pole Standard LeverLock 制造商:OTTO Engineering Inc 功能描述:1 POLE, SCREW, STD, |

| T7-121A2G | 功能描述:撥動開關 ON NONE OFF 1 Pole Standard LeverLock RoHS:否 制造商:OTTO 觸點形式: 開關功能: 電流額定值: 電壓額定值 AC: 電壓額定值 DC: 功率額定值: 端接類型: 安裝風格: 端子密封: 觸點電鍍: 照明: |

| T7-121A5 | 制造商:OTTO 功能描述:Toggle Switches ON NONE OFF 1 Pole Standard Bat Handle 制造商:OTTO Engineering Inc 功能描述:Switch Toggle ON None OFF SPST Bat Toggle Screw 16A 115VAC 28VDC Panel Mount with Threads |

| T7-121B1 | 功能描述:撥動開關 ON NONE ON 1 Pole Standard Bat Handle RoHS:否 制造商:OTTO 觸點形式: 開關功能: 電流額定值: 電壓額定值 AC: 電壓額定值 DC: 功率額定值: 端接類型: 安裝風格: 端子密封: 觸點電鍍: 照明: |

發(fā)布緊急采購,3分鐘左右您將得到回復。