- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371180 > T8531 T8502 and T8503 Dual PCM Codecs with Filters PDF資料下載

參數(shù)資料

| 型號(hào): | T8531 |

| 元件分類: | Codec |

| 英文描述: | T8502 and T8503 Dual PCM Codecs with Filters |

| 中文描述: | T8502和T8503雙的PCM編解碼器與濾波器 |

| 文件頁(yè)數(shù): | 10/48頁(yè) |

| 文件大?。?/td> | 999K |

| 代理商: | T8531 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)

10

Lucent Technologies Inc.

Preliminary Data Sheet

November 2000

Codec Chip Set

T8531/T8532 Multichannel Programmable

Pin Information

(continued)

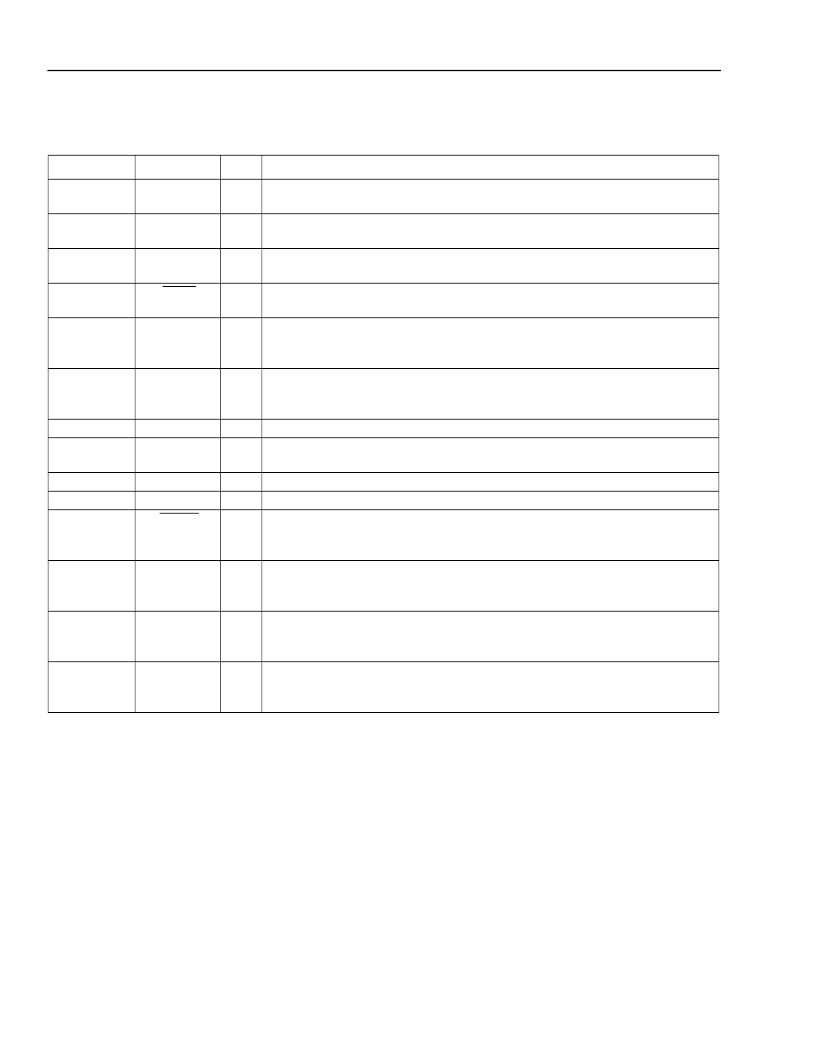

Table 2. T8531 Pin Descriptions

Note: TI = TTL input, TO = TTL output; CI = CMOS input, CO = CMOS output; AI = analog input, AO = analog output; I

u

indicates a pull-up

device is included on this lead.

Number

29

Name

UPDI

Type

TI

Name/Function

Control Data Interface Input.

The microcontroller sends control register

address and data to the T8531 through this pin.

Control Data Interface Output.

The microcontroller receives control regis-

ter contents from this pin. Inactive state is high impedance.

Control Data Interface Clock.

Bit clock for the control interface. Speed is

limited to 4.096 MHz.

Control Interface Chip Select (Active-Low).

This active-low input enables

the control interface.

Oversampled Transmit Data.

Four channels of 1 Msamples/s

Σ

-

transmit

data are received from the T8532 chips through each of these pins. The data

rate is 4.096 MHz.

Oversampled Receive Data.

Four channels of 1 Msamples/s

Σ

-

receive

data is transmitted to the T8532 chips on each of these pins. The data rate is

4.096 MHz.

4.096 MHz Clock.

Clock for data transfer to/from T8532 chips.

Oversampling Sync.

8 kHz synchronization pulse for data transfer

to/from T8532 chips.

Synthesizer V

DD

.

Power supply for clock synthesizer block.

Synthesizer Ground.

Ground connection for the clock synthesizer block.

Backplane Drive Enable (Active-Low).

Active when SDX is transmitting

valid data; high impedance otherwise. This pin provides an enable signal for

a backplane line driver.

Master Clock Input.

This is the bit clock used to shift data into and out of the

SDR and SDX pins. It is the input to the clock synthesizer and is used to

generate all internal clocks. Rate is 4.096 MHz.

Master Clock Select Input.

A logic low selects the 2.048 MHz SCK. A logic

high selects the 4.096 MHz SCK. An internal pull-up device is included, pro-

viding 4.096 MHz SCK operation with no external connections.

Receive PCM Input.

The data on this pin is shifted into the T8531 on the

falling edges of SCK. Data is only entered for valid time slots as defined in

the TSA registers.

30

UPDO

TO

27

UPCK

TI

28

UPCS

TI

43, 45,

36, 38

OSDX[3:0]

CI

42, 44,

35, 37

OSDR[3:0]

CO

39

40

OSCK

OSFS

CO

CO

11

13

24

V

DDA

V

SSA

STSXB

—

—

TO

20

SCK

TI

17

SCKSEL

TI

u

22

SDR

TI

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T8532 | T8502 and T8503 Dual PCM Codecs with Filters |

| T8533 | T8533/34 Quad Programmable Line Card Signal Processor |

| T8534 | T8533/34 Quad Programmable Line Card Signal Processor |

| T8535B | T8535B/T8536B Quad Programmable Codec |

| T8536B | T8535B/T8536B Quad Programmable Codec |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T8531A | 制造商:AGERE 制造商全稱:AGERE 功能描述:T8531A/8532 Multichannel Programmable Codec Chip Set |

| T8532 | 制造商:AGERE 制造商全稱:AGERE 功能描述:T8531A/8532 Multichannel Programmable Codec Chip Set |

| T8533 | 制造商:AGERE 制造商全稱:AGERE 功能描述:T8533/34 Quad Programmable Line Card Signal Processor |

| T85331G | 制造商:BITECH 制造商全稱:Bi technologies 功能描述:Thick Film Super Low Profile SIP Resistor Networks |

| T85331J | 制造商:BITECH 制造商全稱:Bi technologies 功能描述:Thick Film Super Low Profile SIP Resistor Networks |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。