- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371180 > T8531 T8502 and T8503 Dual PCM Codecs with Filters PDF資料下載

參數(shù)資料

| 型號(hào): | T8531 |

| 元件分類: | Codec |

| 英文描述: | T8502 and T8503 Dual PCM Codecs with Filters |

| 中文描述: | T8502和T8503雙的PCM編解碼器與濾波器 |

| 文件頁數(shù): | 15/48頁 |

| 文件大小: | 999K |

| 代理商: | T8531 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

Lucent Technologies Inc.

15

Preliminary Data Sheet

November 2000

Codec Chip Set

T8531/T8532 Multichannel Programmable

Chip Set Functional Description

(continued)

T8531 Functional Blocks

(continued)

T8531 System Interface

The system interface is a full-duplex interface used for

the exchange of PCM data with the system. The sys-

tem is the master of this bus. No control information is

transmitted over the system interface; all control

instructions are routed over the microprocessor inter-

face.

The system interface is used for all 16 lines serviced by

the T8531. The PCM data rate is 8 ksamples/s/line,

so the total required channel capacity is 16 x 8 =

128 Kwords/s in each direction. At the 4.096 MHz rate,

each word takes 1.95

μ

s to transmit interleaved with

5.86

μ

s of dead time. The frame sync, SFS, is pre-

sented to the system interface at an 8 kHz rate.

A single bit clock and frame sync are used to control

both the transmit and receive directions. The beginning

of the first time slot in a frame is identified from the SFS

input (see Figure 9). In nondelayed mode, SFS is

active coincident with bit 0 of time slot 0 of the RX

frame (and the TX frame if the programmed offset

between TX and RX is 0). In delayed mode, SFS is

active one cycle earlier.

The amount of skew or offset between the transmit and

receive frames and time slots is programmable via

board control word 2, 0x1FFC. The bit offset is up to a

frame, i.e., up to 511 bits in 4 MHz mode. The bit offset

skew takes place in the system PCM interface block.

The active transmit and receive time slots are deter-

mined by the card address. The number of time slots

within a frame varies according to the rate of SCK. Only

16 time slots are ever active in a frame, as shown in

Table 3.

The T8531 obtains its card address in board control

word 1, 0x1FFE.

In

μ

-law or A-law mode, each PCM word is only 8 bits

long and occupies one time slot. In linear mode, the

PCM word is 16 bits long and occupies two adjacent

time slots. The MSB is the first bit clocked out in the

valid time slot, and the LSB is the last bit of the follow-

ing (invalid) time slot.

T8531 Microprocessor Interface

This interface between the microprocessor (or other

external controller) and the T8531 device carries user-

supplied program variables and control and test

instructions to both the T8531 and the T8532 octal

converters. The external device is the master of the

microprocessor interface. The interface is serial and

asynchronous, and consists of four pins (UPCK,

UPCS, UPDI, UPDO). The data rate is determined by

the customer’s choice of external device, but may not

exceed 4.096 MHz. Microprocessor interface com-

mands consist of two words, address and data.

Address and data are 16 bits wide. The T8531 expects

an address first. The first bit of the address word is the

R/W flag, which tells the T8531 whether it must receive

or send data (receive, R/W = 0; send, R/W = 1).

Addresses less than 0x1400 refer to the DSP engine

RAM space. If a read from the DSP engine is required,

the microprocessor interface issues a read interrupt to

the DSP engine. If it's a write to the DSP engine, the

microprocessor interface shifts in the data word and

saves it into the data register before sending a write

interrupt to the DSP engine. Once in every 7.8

μ

s time

segment, the DSP engine checks whether an interrupt

is outstanding from the microprocessor interface block.

If so, the DSP engine reads the address register. If it's

a read, the DSP engine fetches the word from RAM,

places it in the data register, and shifts it out to the

microprocessor. If it's a write, it puts the contents of the

data register into RAM.

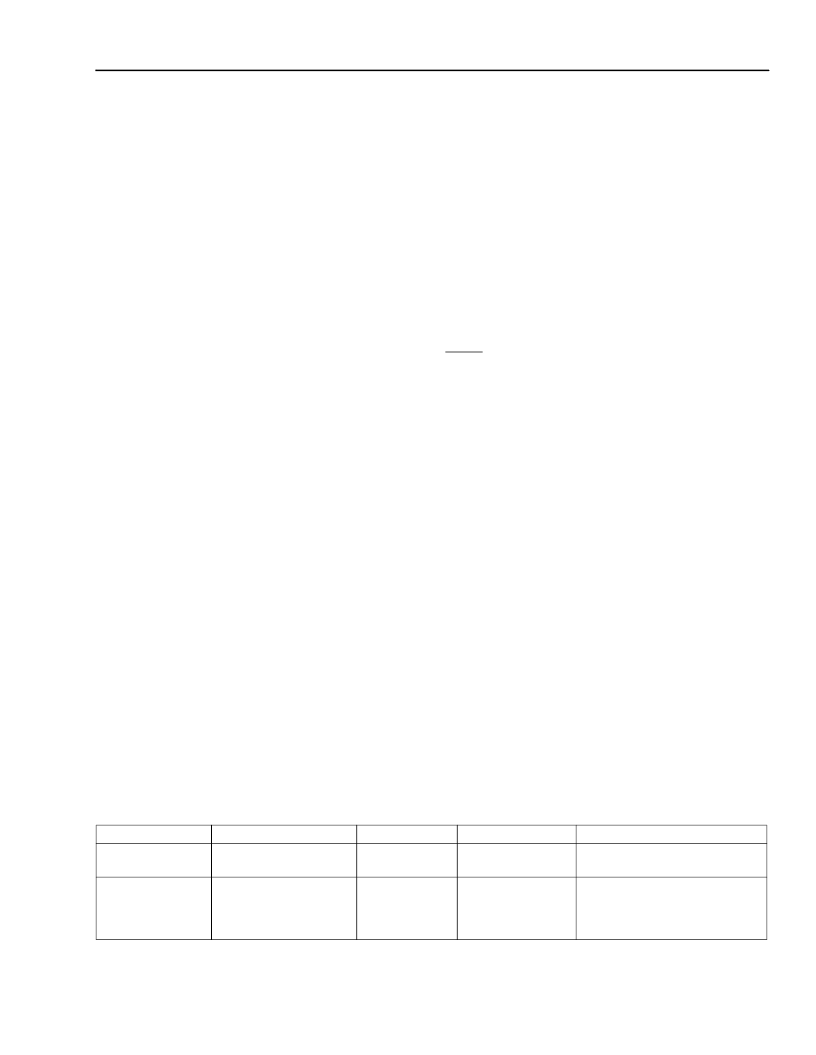

Table 3. Active Time-Slot Spacing in a PCM Bus Frame

SCK Rate (MHz)

2.048

Total # of Time Slots

32

Card Address

0

1

0

1

2

3

Valid Time Slots

0, 2, 4, . . . 30

1, 3, 5, . . . 31

0, 4, 8, . . . 60

1, 5, 9, . . . 61

2, 6, 10, . . . 62

3, 7, 11, . . . 63

Invalid Time Slots

1, 3, 5, . . . 31

0, 2, 4, . . . 30

1—3, 5—7, . . . 61—63

0, 2—4, 6—8, . . . 62—63

0—1, 3—5, 7—9, . . . 63

0—2, 4—6, 8—10, . . . 60—62

4.096

64

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T8532 | T8502 and T8503 Dual PCM Codecs with Filters |

| T8533 | T8533/34 Quad Programmable Line Card Signal Processor |

| T8534 | T8533/34 Quad Programmable Line Card Signal Processor |

| T8535B | T8535B/T8536B Quad Programmable Codec |

| T8536B | T8535B/T8536B Quad Programmable Codec |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T8531A | 制造商:AGERE 制造商全稱:AGERE 功能描述:T8531A/8532 Multichannel Programmable Codec Chip Set |

| T8532 | 制造商:AGERE 制造商全稱:AGERE 功能描述:T8531A/8532 Multichannel Programmable Codec Chip Set |

| T8533 | 制造商:AGERE 制造商全稱:AGERE 功能描述:T8533/34 Quad Programmable Line Card Signal Processor |

| T85331G | 制造商:BITECH 制造商全稱:Bi technologies 功能描述:Thick Film Super Low Profile SIP Resistor Networks |

| T85331J | 制造商:BITECH 制造商全稱:Bi technologies 功能描述:Thick Film Super Low Profile SIP Resistor Networks |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。