- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385899 > TAS5036IPFCR (Texas Instruments, Inc.) SIX CHANNEL DIGITAL AUDIO PWM PROCESSOR PDF資料下載

參數(shù)資料

| 型號: | TAS5036IPFCR |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | SIX CHANNEL DIGITAL AUDIO PWM PROCESSOR |

| 中文描述: | 六聲道數(shù)字音頻PWM處理器 |

| 文件頁數(shù): | 20/49頁 |

| 文件大小: | 642K |

| 代理商: | TAS5036IPFCR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁

Architecture Overview

15

SLES044B

—

November 2002

TAS5036

2.2

Reset, Power Down, and Status

The reset, power down, and status circuitry provides the necessary controls to bring the TAS5036 to the initial

inactive condition, achieve low power standby, and report system status.

2.2.1 Reset—RESET

The TAS5036 is placed in the reset mode by setting the RESET terminal low.

RESET is an asynchronous control signal that restores the TAS5036 to its default conditions, sets the valid

1

–

6 outputs low, and places the PWM in the hard mute state. Volume is immediately set to full attenuation

(there is no ramp down).

As long as the RESET terminal is held low, the device is in the reset state. During reset, all I

2

C and serial data

bus operations are ignored. Table 2

–

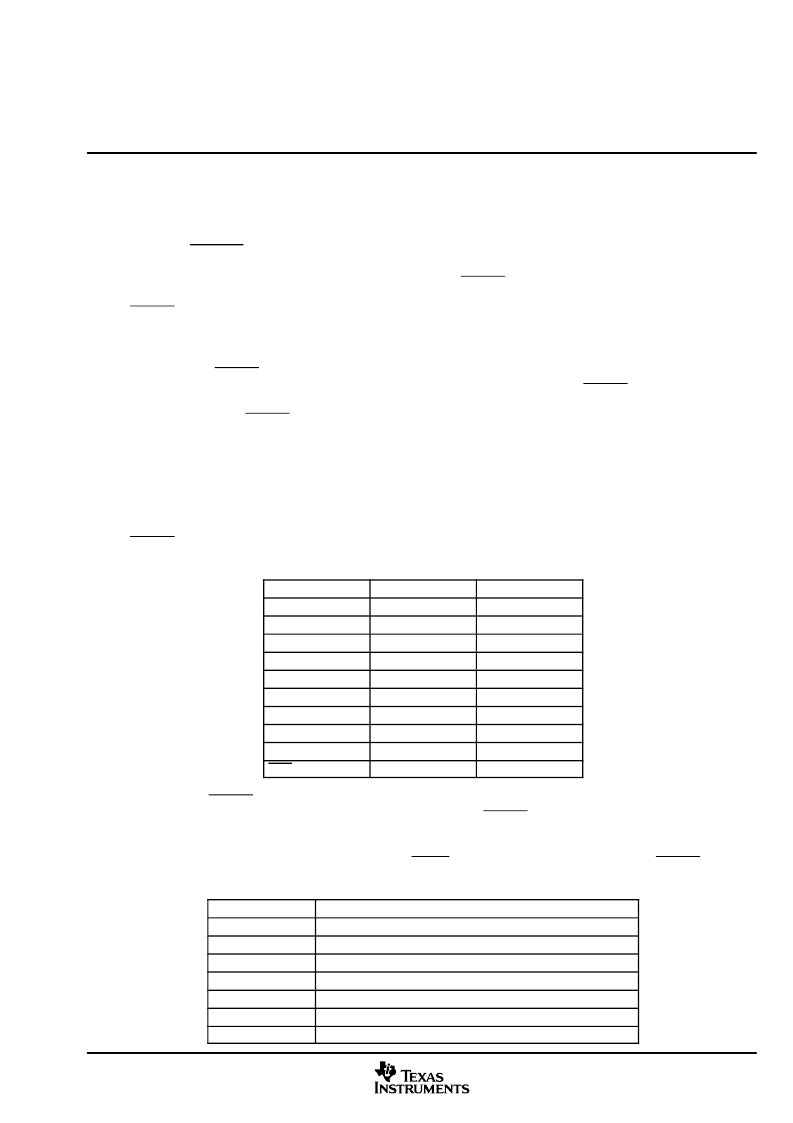

6 shows the device output signals while RESET is active.

Upon the release of RESET, if POWER_DWN is high, the system performs a 4-ms to 5-ms device initialization

and then ramps the volume up to 0 db using a soft volume update sequence. If MCLK_IN is not active when

RESET is released high, then a 4-ms to 5-ms initialization sequence is produced once MCLK_IN becomes

active.

During device initialization all controls are reset to their initial states. Table 2

–

7 shows the control settings that

are changed during initialization.

RESET should be applied during power-up initialization or while changing the master slave clock states.

Table 2

–

6. Device Outputs During Reset

SIGNAL

MODE

SIGNAL STATE

Valid 1

–

Valid 6

All

Low

PWM P-outputs

All

Low

PWM M-outputs

All

Low

MCLKOUT

All

Low

SCLK

Master

Low

SCLK

Slave

Signal input

LRCLK

Master

Low

LRCLK

Slave

Signal input

SDA

All

Signal input

CLIP

All

High

Because the RESET is an asynchronous control signal, small clicks and pops can be produced during the

application (the leading edge) of this control. However, when RESET is released, the transition from the hard

mute state back to normal operation is performed synchronously using a quiet sequence.

If a completely quiet reset sequence is desired, MUTE should be applied before applying RESET.

Table 2

–

7. Values Set During Reset

CONTROL

SETTING

Volume

0 dB

MCLK_IN frequency

256

Master/slave mode

M_S terminal state

Auto mute

Enabled

De-emphasis

None

DC offset

0

Interchannel delay

Each channel set at 16 clocks higher then preceding channel

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TB1239BF | Bi-CMOS Integrated Circuit Silicon Monolithic |

| TB1240AN | PAL/NTSC 1CHIP (IF + VCD RPOCESSOR) IC |

| TB1245N | TOSHIBA Bi-CMOS INTEGRATED CIRCUIT SILICON MONOLITHIC |

| TB1261F | TOSHIBA BiCMOS INTEGRATED CIRCUIT, SILICON MONOLITHIC |

| TB1262F | TOSHIBA BiCMOS INTEGRATED CIRCUIT, SILICON MONOLITHIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TAS5036IPFCRG4 | 功能描述:音頻 DSP Digital Audio PWM Processor RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風格: 封裝 / 箱體: 封裝:Tube |

| TAS5036PFC | 制造商:TI 制造商全稱:Texas Instruments 功能描述:SIX CHANNEL DIGITAL AUDIO PWM PROCESSOR |

| TAS5036PFCR | 制造商:TI 制造商全稱:Texas Instruments 功能描述:SIX CHANNEL DIGITAL AUDIO PWM PROCESSOR |

| TAS5066 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:SIX-CHANNEL Digital Audio PWM Processor |

| TAS5066-5111D6EVM | 功能描述:音頻 IC 開發(fā)工具 TAS5066-5111D6 EVAL MOD RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Kits 類型:Audio Amplifiers 工具用于評估:TAS5614L 工作電源電壓:12 V to 38 V |

發(fā)布緊急采購,3分鐘左右您將得到回復。