- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98252 > TLV320AIC13I (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PDSO30 PDF資料下載

參數(shù)資料

| 型號: | TLV320AIC13I |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PDSO30 |

| 封裝: | PLASTIC, SOP-30 |

| 文件頁數(shù): | 13/55頁 |

| 文件大小: | 455K |

| 代理商: | TLV320AIC13I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁

3–7

SCLK

FS

DIN/DOUT

(16 Bit)

MSB

LSB

D15

D14

D1

D0

0

1

15

16

14

D15

16 SCLKs

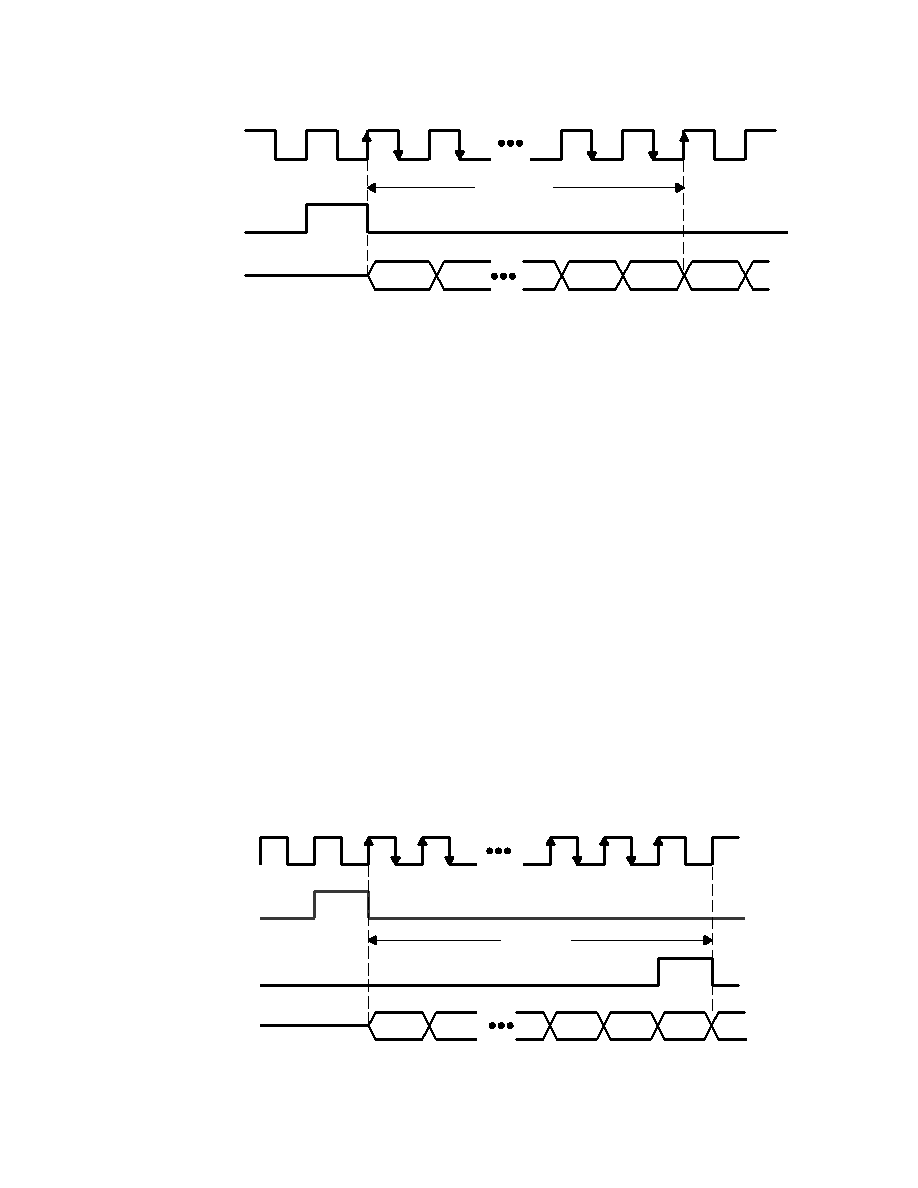

Figure 3–6. Timing Diagram of FS

3.6.5

Cascade Mode and Frame-Sync Delayed (FSD)

In cascade mode, the DSP receives all frame-sync pulses from the master though the master’s FS. The master’s FSD

is output to the first slave and the first slave’s FSD is output to the second slave device and so on. Figure 3–8 shows

the cascade of 4 TLV320AIC13s in which the closest one to DSP is the master and the rest are slaves. The FSD output

of each device is input to the FS terminal of the succeeding device. Figure 3–9 shows the FSD timing sequence in

the cascade.

3.6.6

Stand-Alone Slave

In the stand-alone slave connection, the FS and SCLK are input in which they need to be synchronized to each other

and programmed according to Section 3.1 (Operating Frequencies). The FS and SCLK input are not required to

synchronize to the MCLK input but must remain active at all times to assure continuous sampling in the data converter.

FS is output for initial 132 MCLK and it must be kept low. DSP needs to keep FS low or high-impedance state for this

period to avoid contention on FS.

3.6.7

Asynchronous Sampling

(CODECs in cascade are sampled at different sampling frequency)

The AIC13s SMARTDM support different sampling frequency between the different codecs in cascade connecting

to a single to serial port in which all codecs is sampled at the same frequency of FS as followed. For example: fs1

and fs2 are desired sampling rates for CODEC1 and CODEC2 respectively:

1.

FS = MCLK/(16xMxNxP)

2.

FS = n1 x fs1 (n1 = 1,2, 0, 8 defined in the control register 3 of CODEC1)

3.

FS = n2 x fs2 (n2 = 1,2, 0, 8 defined in the control register 3 of CODEC2)

For validating the conversion data from this operation:

For DAC: DSP need to give same data for n1 samples. CODEC1 picks one of n1 samples.

For ADC: CODEC1 gives same data for n1 samples. DSP should pick one of n1 samples.

SCLK

FSD

(Output)

DIN/DOUT

(16 Bit)

MSB

LSB

D15

D14

D2

D1

0

1

14

15

13

D0

FS

16 SCLKs

D15

MSB

Figure 3–7. Timing Diagram for FSD Output

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV320AIC14C | SPECIALTY CONSUMER CIRCUIT, PDSO30 |

| TLV320AIC14I | SPECIALTY CONSUMER CIRCUIT, PDSO30 |

| TLV320AIC22PT | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TLV320AIC22PTR | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TLV320AIC23BGQE | SPECIALTY CONSUMER CIRCUIT, PBGA80 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV320AIC13IDBT | 功能描述:接口—CODEC Lo-Pwr Mono Voice Band CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC13IDBTG4 | 功能描述:接口—CODEC Lo-Pwr Mono Voice Band CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC13IDBTR | 功能描述:接口—CODEC Lo-Pwr Mono Voice Band CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC13IDBTRG4 | 功能描述:接口—CODEC Lo-Pwr Mono Voice Band CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC14 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:LOW-POWER, HIGHLY-INTEGRATED, PROGRAMMABLE 16-Bit, 26-KSPS MONO CODEC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。