- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19457 > TMS320VC5409ZGU-80 (Texas Instruments)IC FIXED POINT DSP 144-BGA PDF資料下載

參數(shù)資料

| 型號: | TMS320VC5409ZGU-80 |

| 廠商: | Texas Instruments |

| 文件頁數(shù): | 31/93頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FIXED POINT DSP 144-BGA |

| 標準包裝: | 160 |

| 系列: | TMS320C54x |

| 類型: | 定點 |

| 接口: | 主機接口,McBSP |

| 時鐘速率: | 80MHz |

| 非易失內(nèi)存: | ROM(32 kB) |

| 芯片上RAM: | 64kB |

| 電壓 - 輸入/輸出: | 3.30V |

| 電壓 - 核心: | 1.80V |

| 工作溫度: | -40°C ~ 100°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 144-LFBGA |

| 供應商設(shè)備封裝: | 144-BGA MICROSTAR(12x12) |

| 包裝: | 托盤 |

| 配用: | 296-15829-ND - DSP STARTER KIT FOR TMS320C5416 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁

Functional Overview

37

April 1999 Revised October 2008

SPRS082F

This clock generator allows system designers to select the clock source. The sources that drive the clock

generator are:

A crystal resonator circuit. The crystal resonator circuit is connected across the X1 and X2/CLKIN pins

of the 5409 to enable the internal oscillator.

An external clock. The external clock source is directly connected to the X2/CLKIN pin, and X1 is left

unconnected.

The software-programmable PLL features a high level of flexibility, and includes a clock scaler that provides

various clock multiplier ratios, capability to directly enable and disable the PLL, and a PLL lock timer that can

be used to delay switching to PLL clocking mode of the device until lock is achieved. Devices that have a

built-in software-programmable PLL can be configured in one of two clock modes:

PLL mode. The input clock (X2/CLKIN) is multiplied by 1 of 31 possible ratios. These ratios are achieved

using the PLL circuitry.

DIV (divider) mode. The input clock is divided by 2 or 4. Note that when DIV mode is used, the PLL can

be completely disabled in order to minimize power dissipation.

The software-programmable PLL is controlled using the 16-bit memory-mapped (address 0058h) clock mode

register (CLKMD). The CLKMD register is used to define the clock configuration of the PLL clock module. Upon

reset, the CLKMD register is initialized with a predetermined value dependent only upon the state of the

CLKMD1 CLKMD3 pins as shown in Table 311.

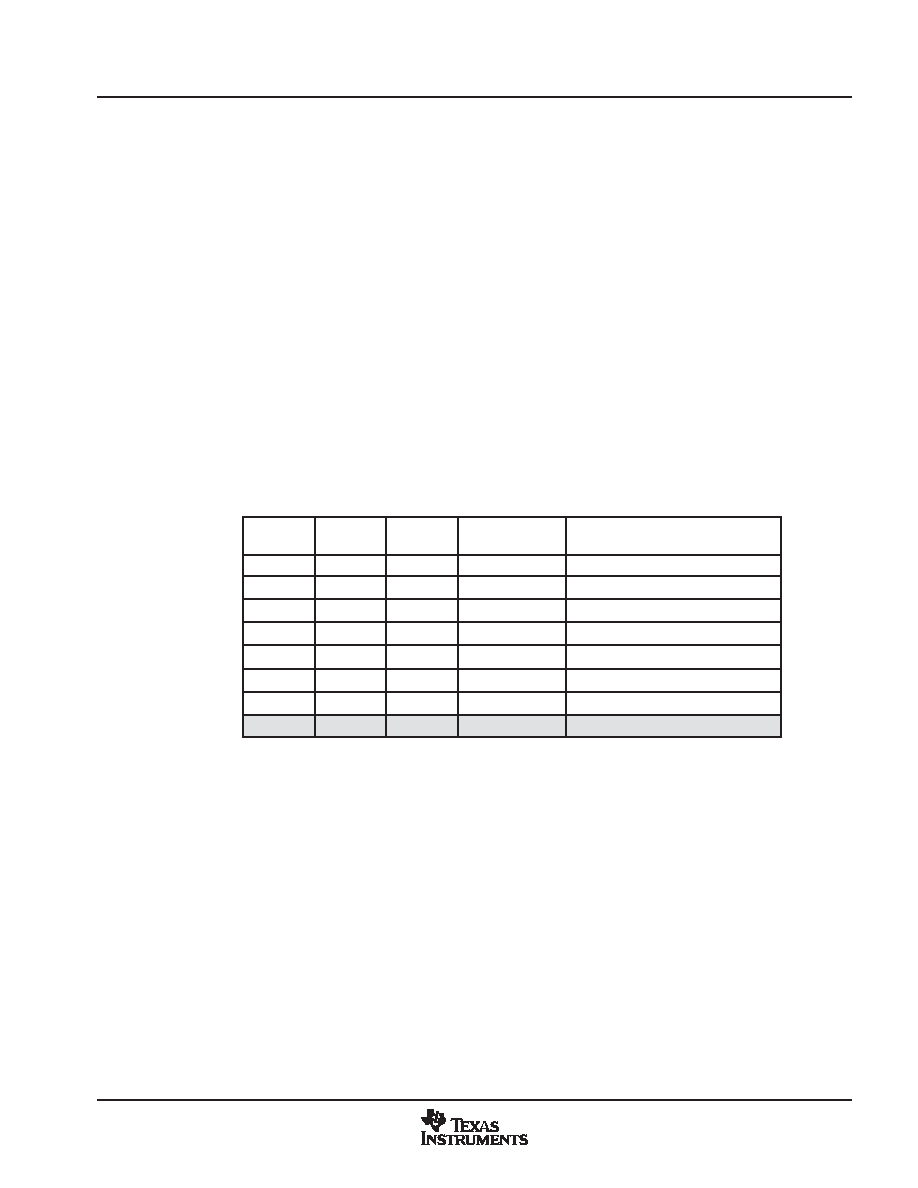

Table 311. Clock Mode Settings at Reset

CLKMD1

CLKMD2

CLKMD3

CLKMD

RESET VALUE

CLOCK MODE

CLKMD1

CLKMD2

CLKMD3

RESET VALUE

CLOCK MODE

0

E007h

PLL x 15

0

1

9007h

PLL x 10

0

1

0

4007h

PLL x 5

1

0

1007h

PLL x 2

1

0

F007h

PLL x 1

1

0000h

1/2 (PLL disabled)

1

0

1

F000h

1/4 (PLL disabled)

0

1

—

Reserved

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AYM30DRSS | CONN EDGECARD 60POS DIP .156 SLD |

| ASM30DRSS | CONN EDGECARD 60POS DIP .156 SLD |

| TMS320VC5409GGU-80 | IC FIXED POINT DSP 144-BGA |

| HSM06DSXH | CONN EDGECARD 12POS DIP .156 SLD |

| AGM30DRSS | CONN EDGECARD 60POS DIP .156 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMS320VC5410AGGU1 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

| TMS320VC5410AGGU12 | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Dig Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風格:SMD/SMT |

| TMS320VC5410AGGU16 | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Dig Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風格:SMD/SMT |

| TMS320VC5410APGE12 | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Dig Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風格:SMD/SMT |

| TMS320VC5410APGE16 | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Dig Sig Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復。